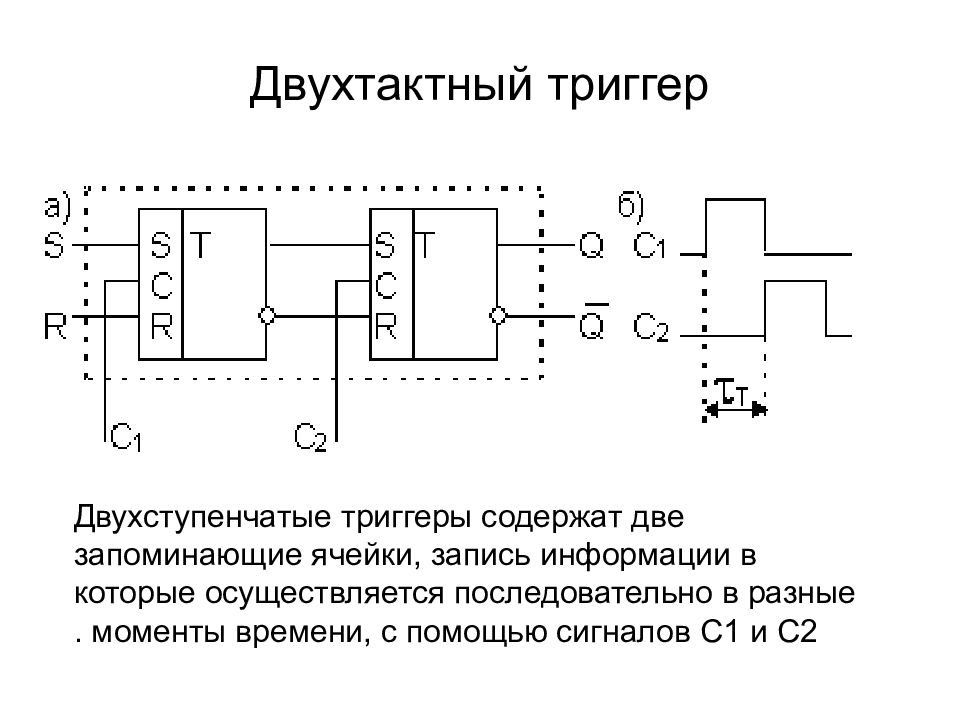

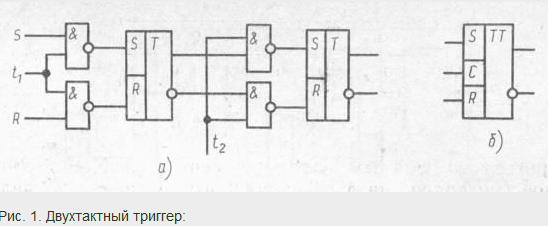

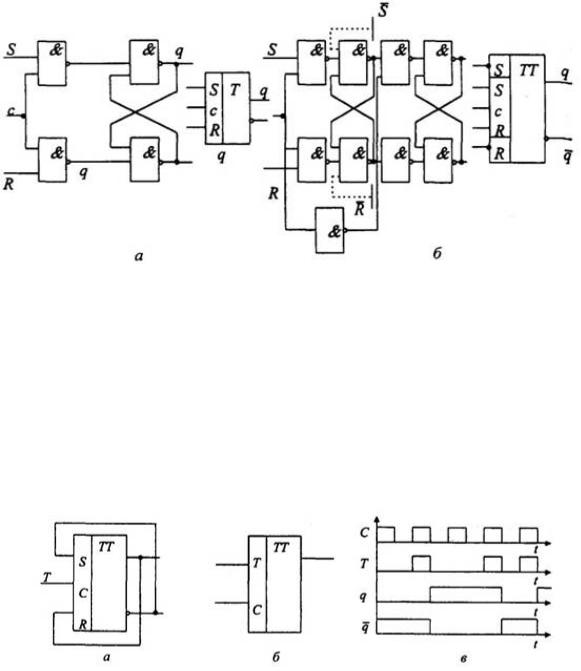

Двухтактные триггеры

К основным недостаткам рассмотренных выше однотактных триггеров следует отнести: срабатывание триггеров по уровню импульса, в результате чего за время тактового импульса, при изменении уровня на информационных входах, триггер меняет свое состояние; наличие аналоговых элементов задержки сильно усложняет схему и накладывает ограничение на её работу (τи < τз в T-триггере).

Исключить эти недостатки позволяют двухтактные триггеры, в которых запоминание информации осуществляется по фронту тактового импульса.

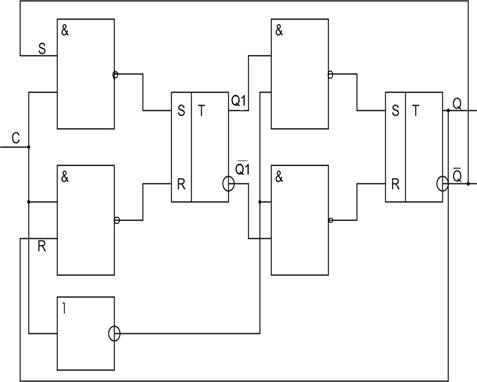

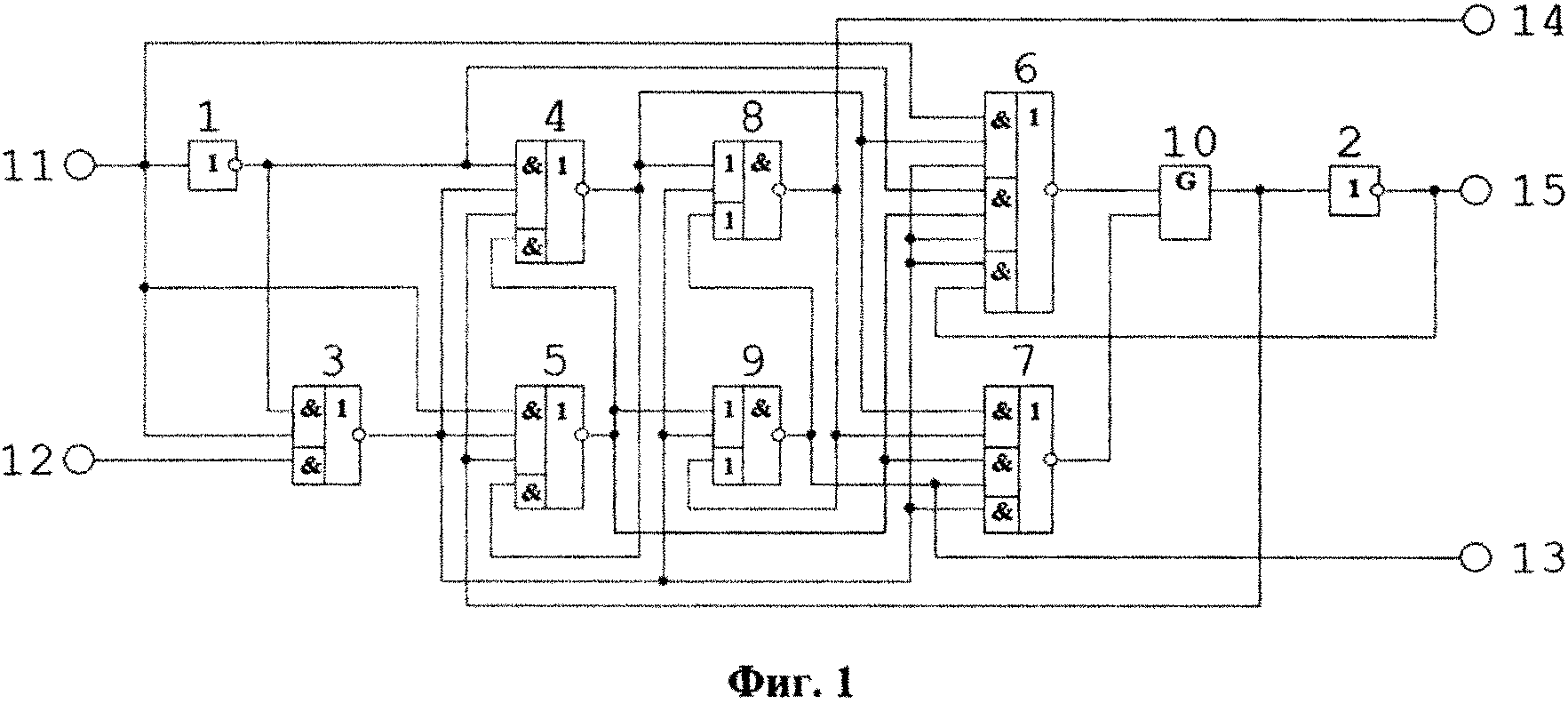

Триггер

T-типа. Двухтактные

триггеры Т-типа

выполняются на базе двух однотактных RS-триггеров,

один из которых называют основным (DD2),

а другой – вспомогательным (DD1).

Особенностью рассматриваемой схемы

является наличие в ней дополнительного

инвертора (DD3),

управляющего вспомогательным триггером

DD1.

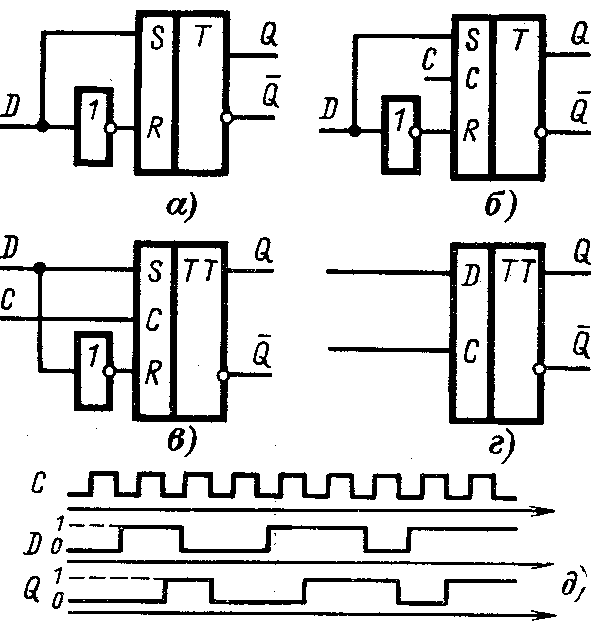

Рис. 3.40. Двухтактный T-триггер (слева) и его временные диаграммы (справа) | |

Пусть в начальный момент триггер DD2 находится в состоянии 0, (рис. 3.35). Тогда через обратные связи на вход R вспомогательного триггера DD1 действует лог.1, а на вход S – лог.0. Как только на тактовый сигнал T подается лог.1, триггер DD1 сбрасывается (). На вход R основного триггера DD2 начинает действовать лог.0, а на вход S – лог.1. Установка сигнала T в низкое состояние приведет к тому, что через инвертор DD3 на тактовый вход основного триггера DD2 будет действовать лог.1. Это приведет к записи в DD2 лог.1, т.е. триггер переключится в противоположное состояние. Таким образом, каждый задний фронт тактового импульса будет приводить к переключению триггера.

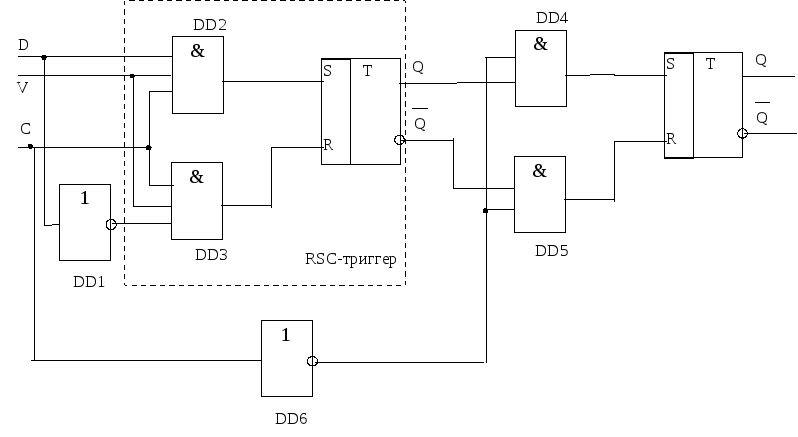

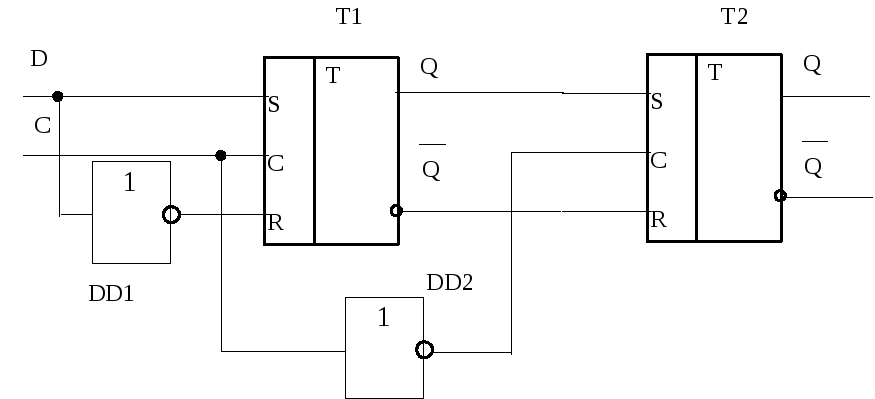

Двухтактный

триггер D-типа. Двухтактные

триггеры D-типа выполняются на базе двух

однотактных D-триггеров, один из которых

называют основным, а другой –

вспомогательным (рис. 3.36). В них

последовательно записывается информация

по двум тактовым импульсам – T1 и T2 . По

импульсу T1 информация записывается в

первый триггер, а затем по импульсу T2

переписывается во второй. В качестве

импульсов T2 обычно используется

инвертированная последовательность

импульсов T1. В результате такой реализации

в триггере обеспечивается задержка

импульсов τз автоматически во время паузы T1. В то же

время осуществляется срабатывание

триггера по фронту импульса, а не по

уровню – как в однотактных схемах. В

этой схеме, в качестве элемента задержки,

используется второй D-триггер, работающий

по импульсам второй последовательности

T2.

Двухтактные

триггеры D-типа выполняются на базе двух

однотактных D-триггеров, один из которых

называют основным, а другой –

вспомогательным (рис. 3.36). В них

последовательно записывается информация

по двум тактовым импульсам – T1 и T2 . По

импульсу T1 информация записывается в

первый триггер, а затем по импульсу T2

переписывается во второй. В качестве

импульсов T2 обычно используется

инвертированная последовательность

импульсов T1. В результате такой реализации

в триггере обеспечивается задержка

импульсов τз автоматически во время паузы T1. В то же

время осуществляется срабатывание

триггера по фронту импульса, а не по

уровню – как в однотактных схемах. В

этой схеме, в качестве элемента задержки,

используется второй D-триггер, работающий

по импульсам второй последовательности

T2.

Пунктиром показана электрическая связь для организации двухтактного счетного триггера.

а) б)

Рис. 3.41. Двухтактный D-триггер

(а)

и его временные диаграммы (б)

3.41. Двухтактный D-триггер

(а)

и его временные диаграммы (б)

Двухтактные триггеры могут работать: по переднему фронту или по заднему фронту. Тактовые входы таких триггеров на УГО обозначаются косой чертой (рис. 3.37).

Рис. 3.42. D-триггер, срабатывающий по переднему (слева) и по заднему (справа) фронту тактового импульса

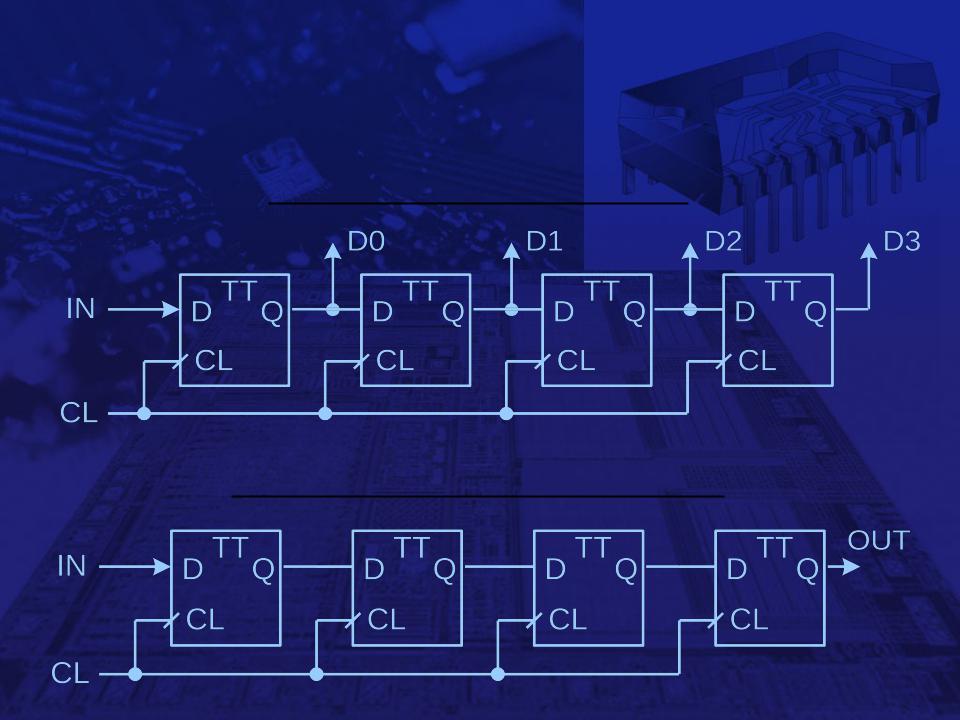

Регистры

Регистрами называются многоразрядные цифровые запоминающие устройства, предназначенные для приёма, хранения, преобразования и передачи информации.

Основу регистра составляют триггеры. Обычно используются D-триггеры, как наиболее удобные для записи и хранения информации. Чаще всего используются двухтактные D-триггеры, в которые запоминание осуществляется по фронту тактового импульса, гораздо реже – RS-триггеры.

Регистры

делятся на параллельные, последовательные и параллельно-последовательные.

Рис. 3.43. Параллельный регистр |

Последовательные

регистры. Последовательные

регистры работают с последовательным

кодом, разряды которого разделены во

времени на интервалы, равные периоду

следования тактового импульса T. Такой

способ представления информации широко

используется при передаче информации

между цифровыми устройствами, что

позволяет экономить количество проводов,

по которым передаётся информация. Недостатком является значительное

время передачи информации.

Недостатком является значительное

время передачи информации.

Различают регистры прямого сдвига и реверсивные регистры. Регистры прямого сдвига осуществляют приём (передачу) информации, сдвигая её в регистре на 1 разряд вправо при приходе одного тактового импульса. Для полного приёма (передачи) информации требуется n тактов. Регистр представляет собой n последовательно соединённых D-триггеров, тактовые входы которых объединены. Имеется один информационный вход I для приёма информации (рис. 3.39). Вход R позволять сбросить все триггеры регистра одновременно.

Реверсивный

сдвиговый регистр позволяет осуществить

сдвиг информации внутри регистра как

вправо, так и влево. Это может потребоваться

для преобразования последующего кода.

Например, если первоначально следовал

старший разряд кода, то после преобразования

первым будет преобразован младший

разряд кода. Для организации реверсивного

режима между входами и выходами триггеров

включаются одноразрядные мультиплексоры

с двумя информационными входами (рис. 3.40).

3.40).

Рис. 3.44. Последовательный регистр прямого сдвига

Вход V управляет направлением сдвига информации. При V = 0 к выходу мультиплексора подключён вход I1 и схема преобразуется в схему со сдвигом информации вправо. При V = 1 к входам мультиплексора подключён вход I2. При этом выход последующего триггера подключается к информационному входу предыдущего, и таким образом при приходе тактовых импульсов осуществляется сдвиг информации влево.

Параллельно-последовательные регистры. Такие регистры служат для преобразования информации с последовательного кода в параллельный или наоборот, а также могут выполнять функции как последовательных, так и параллельных регистров.

Для

организации одновременного наличия

двух режимов (параллельного и

последовательного) чаще пользуются

более простым схемотехническим решением

– между триггерами включают одноразрядный

мультиплексор (рис. 3.41).

3.41).

Рис. 3.46. Параллельно-последовательный регистр

При V = 0 организуется режим параллельного регистра. При этом в мультиплексорах к выходам подключены входы I1, на которые подаётся параллельный код. В момент прихода тактового импульса этот код записывается в регистр. При V = 1 организуется последовательный режим работы со сдвигом информации вправо. В мультиплексорах к выходам подключены входы I2, через которые осуществляется последовательный режим работы. Для организации в этом регистре реверсивного сдвигового режима необходимо между выходами мультиплексора и информационным входом триггера в каждом разряде подключить ещё один одноразрядный мультиплексор (рис. 3.42).

Рис. 3.47. Параллельно-последовательный реверсивный регистр

Память

Запоминающие

устройства (ЗУ) или память предназначены для запоминания некоторого

количества многоразрядных чисел и

представляют собой такое же количество

линейных регистров.

Рис. 3.48. Структурная схема запоминающего устройства:

m – количество разрядов каждого числа; n – разрядность адресного кода

Оперативное

запоминающее устройство (ОЗУ). ОЗУ

используются для многократной перезаписи

в них информации. ОЗУ бывают статические и динамические.

Статические строятся на основе триггеров,

а в динамических в качестве запоминающих

элементов (ЗЭ) используются ёмкости

(конденсаторы), подключённые через

полевой транзистор к шине данных, чтобы

увеличить время разряда.

Рис. 3.49. Фрагмент структурной схемы динамического ОЗУ |

В этом случае в зависимости от режима

работы можно либо считать информацию,

либо записать новую.

В этом случае в зависимости от режима

работы можно либо считать информацию,

либо записать новую.К ШД подключен затвор транзистора VT2, выполняющего роль усилителя считывания. После подключения нужного конденсатора к ШД с выхода усилителя снимается напряжение, пропорциональное исходному напряжению на конденсаторе СП. ШД имеет большую собственную емкость СШ. Как правило, выполняется условие СШ > СП. Подключение к ШД конденсатора малой емкости за счет перераспределения зарядов емкостей СШ и СП незначительно изменяет ее потенциал. Для распознания этого изменения необходимо очень точно знать исходное напряжение шины, которое в процессе работы может принимать произвольное значение. Поэтому процесс считывания информации предполагает следующую последовательность действий:

– непосредственно перед считыванием информации фиксируют уровень напряжения ШД, для чего при помощи ключа VT3 емкость СШ заряжают до напряжения питания;

– на нужный запоминающий элемент подают сигнал выборки CS; СП подключается к СШ, что сопровождается перераспределением заряда и соответствующим изменением напряжения на ШД;

–

с выхода усилителя считывают сигнал,

пропорциональный заряду конденсатора

выбранного запоминающего элемента.

Считывание информации сопровождается ее разрушением. Запись информации выполняется с использованием транзисторов VT3 и VT4, которые по сигналу управления подключают ШД либо к источнику питания, либо к общей шине. При выборке нужного запоминающего элемента его конденсатор заряжается до напряжения ШД.

Реальная структура ИС динамического ОЗУ много сложнее показанного упрощенного варианта. Она содержит регистры и цепи управления процессами регенерации, а также дополнительную матрицу запоминающих элементов, использующуюся в качестве эталона. Для регенерации по сигналу с блока управления содержимое целой строки матрицы переписывается в регистр и обратно, за счет чего поддерживается требуемый уровень напряжения на конденсаторах памяти.

Постоянные запоминающие

устройства (ПЗУ). ПЗУ

предназначены для длительного хранения

записанной в них информации без

перезаписи. Они

бывают масочные

(информация в них записывается

непосредственно в процессе их

изготовления), с однократным

программированием (обычно путём

прожигания информации) и с многократным

программированием (ультрафиолетовое

или электрическое стирание информации).

Особенностью ПЗУ является отсутствие входов записи информации (программирование или прожигание осуществляется через выходы регистра, а в качестве запоминающих элементов обычно используют диоды или транзисторы в режиме инвертирующего повторителя).

На рисунке 3.45 приведена схема простейшего ПЗУ с организацией 4×8. Она включает дешифратор с двумя адресными шинами, восемь балластных резисторов Rб1-Rб8 выходных шин и диоды, число которых равно числу логических 1, записанных в ПЗУ.

Рис. 3.50. ПЗУ с организацией 4×8

Работа

ПЗУ сводится к следующему. После появления

на выходе дешифратора напряжения

высокого уровня, при наличии связи через

диод между адресной шиной и шиной данных,

это напряжение прикладывается к

соответствующему балластному резистору,

что воспринимается как появление на

шине сигнала логической единицы. При

отсутствии связи ток через соответствующий

резистор не протекает, что классифицируется

как сигнал логического нуля.

а) б) |

Рис. 3.51. Фрагменты масочных ПЗУ на биполярных (а) и полевых (б) транзисторах |

В

ПЗУ с однократным программированием

первоначально имеется связь между шиной

дешифрованного адреса и шиной данных

для всех запоминающих элементов. Процесс

записи осуществляется путем разрушения

(пережигания) специально для этого

предусмотренных перемычек между шинами

дешифрированного адреса и выходными

выводами. Такие перемычки изготавливаются

из нихрома, поликремния или титаната

вольфрама и имеют собственное сопротивление

в несколько десятков Ом. Перемычка

обычно включается в эмиттерную цепь

транзистора. При программировании для

разрушения такой перемычки через

транзистор достаточно пропустить

импульс тока в 20…30 мА при длительности

порядка 1мс. В нормальном режиме работы

токи схемы существенно меньше необходимых

для программирования, поэтому записанная

информация при чтении не разрушается.

Перемычка

обычно включается в эмиттерную цепь

транзистора. При программировании для

разрушения такой перемычки через

транзистор достаточно пропустить

импульс тока в 20…30 мА при длительности

порядка 1мс. В нормальном режиме работы

токи схемы существенно меньше необходимых

для программирования, поэтому записанная

информация при чтении не разрушается.

Рис. 3.52. Запоминающий элемент репрограммируемого ПЗУ |

Транзистор

VT1 служит для выбора по сигналу с выхода

дешифратора адреса соответствующего

транзистора памяти – VT2. Шина через

ограничительный резистор подключена

к выводу источника питания. При отпирании

транзистора VT1 протекание тока в цепи

его стока зависит от состояния транзистора

VT2. Наличие или отсутствие тока

классифицируется как хранение сигналов

логический 0 или логическая 1. Обычно,

если ток в цепи стока VT2 протекает,

считают, что в ячейке был записан сигнал

логический 0, если ток отсутствует –

сигнал логическая 1.

Шина через

ограничительный резистор подключена

к выводу источника питания. При отпирании

транзистора VT1 протекание тока в цепи

его стока зависит от состояния транзистора

VT2. Наличие или отсутствие тока

классифицируется как хранение сигналов

логический 0 или логическая 1. Обычно,

если ток в цепи стока VT2 протекает,

считают, что в ячейке был записан сигнал

логический 0, если ток отсутствует –

сигнал логическая 1.

Последовательностные системы — триггеры

Последовательностные системы — триггеры| Справочное руководство по Electronics Workbench |

3.3.1 Последовательностные системы — триггеры

Раздел: Цифровая схемотехника

Теоретическое введение:

Триггер — цифровой автомат,

имеющий два устойчивых состояния равновесия либо 0, либо 1. на его инверсном

выходе).

на его инверсном

выходе).

Законы функционирования триггеров задаются таблицами переходов с компактной записью, при которой в столбце состояний может быть указано, что новое состояние совпадает с предыдущим либо является его отрицанием

Типы триггеров.

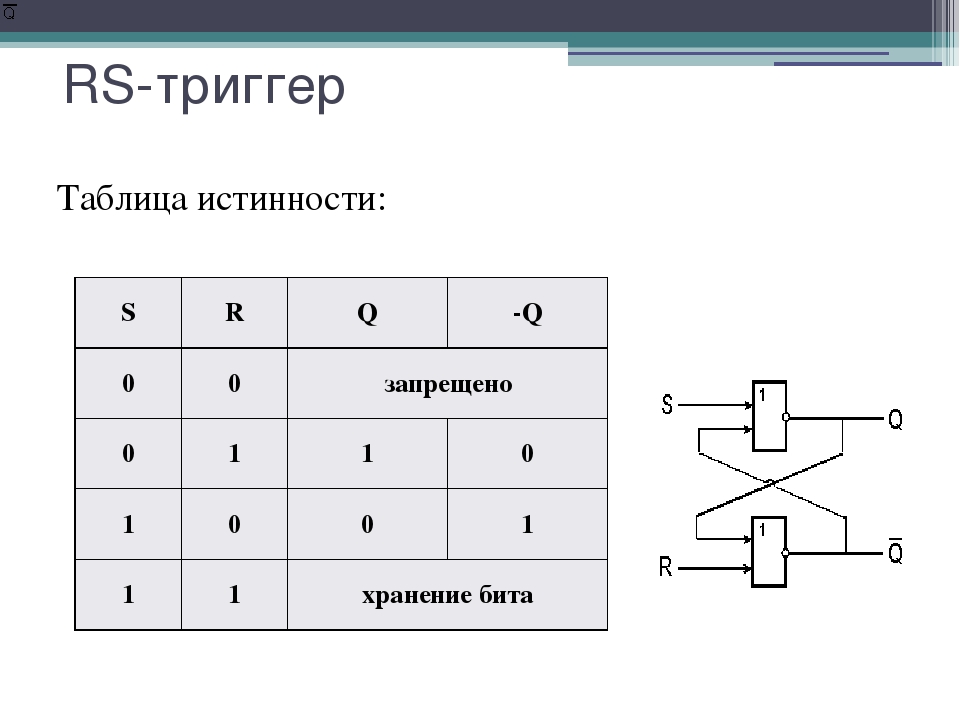

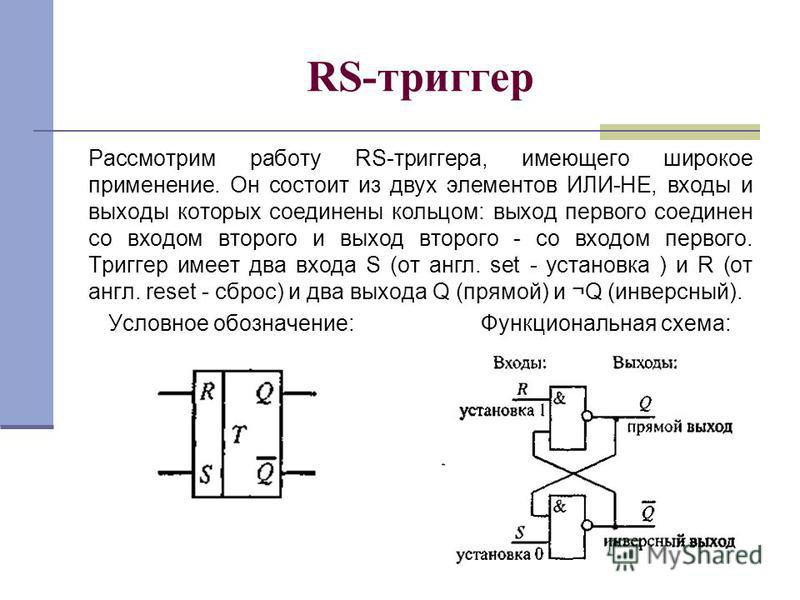

Триггер типа RS имеет два входа раздельной установки в нулевое и единичное состояния. Воздействие по входу S (обозначен по первой букве слова set – установка) приводит триггер в единичное состояние, а воздействие по входу R (от первой буквы слова reset – сброс) – в нулевое. Одновременная подача сигналов S и R не допускается, что является недостатком для RS-триггера.

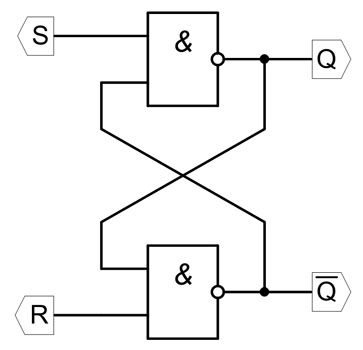

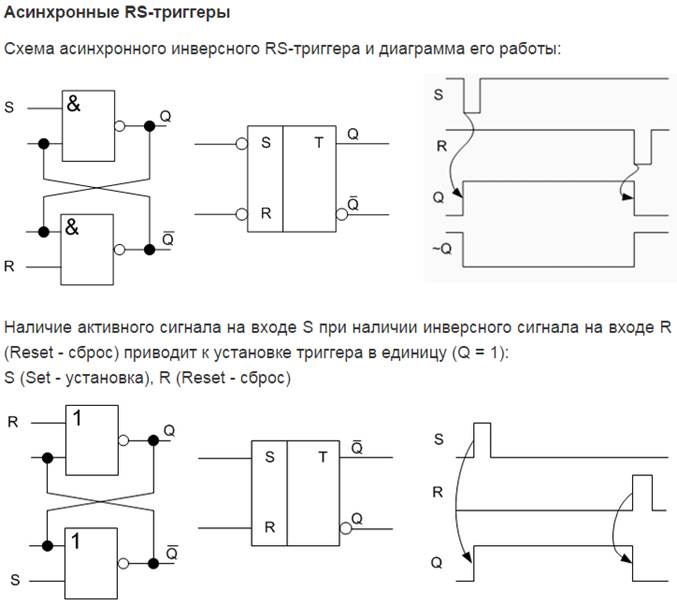

Асинхронный RS-триггер на

элементах И-НЕ показан на рисунке 3.3.1.1. Триггер

образован из двух комбинационных схем И-НЕ, соединенных таким образом, что

возникают положительные обратные связи, благодаря которым в устойчивом состоянии

выходной транзистор одной схемы ИЛИ-НЕ закрыт, а другой открыт. Таблица 3.1.1.1 определяет закон функционирования триггера. На рисунке 3.3.1.2 приведена временная диаграмма иллюстрирующая

работу асинхронного RS-триггера.

Таблица 3.1.1.1 определяет закон функционирования триггера. На рисунке 3.3.1.2 приведена временная диаграмма иллюстрирующая

работу асинхронного RS-триггера.

Рисунок 3.3.1.1 — Схема асинхронного RS-триггера на элементах И-НЕ

|

R |

S |

Q |

Примечание |

|

0 |

0 |

Q |

Хранение |

|

0 |

1 |

1 |

Установка 1 |

|

1 |

0 |

0 |

Установка 0 |

|

1 |

1 |

— |

Запрещено |

Таблица 3. 3.1.1 — Таблица переходов асинхронного

RS-триггера на элементах ИЛИ-НЕ

3.1.1 — Таблица переходов асинхронного

RS-триггера на элементах ИЛИ-НЕ

Рисунок 3.3.1.2 — Диаграмма работы асинхронного RS-триггера

При R=1 и S=0 триггер устанавливается в нулевое состояние Q=0; при R=0 и S=1 он устанавливается в единичное состояние Q=1; при R=S=0 триггер сохраняет состояние, в котором он находился до момента поступления на его входы нулевых сигналов. При R=S=1 на прямом и инверсном выходах устанавливается нулевой сигнал. Триггероное кольцо превращается в два независимых инвертора, и при переходе к хранению (R=S=0) триггер может устанавливаться в любое состояние. Поэтому такая комбинация входных сигналов запрещена.

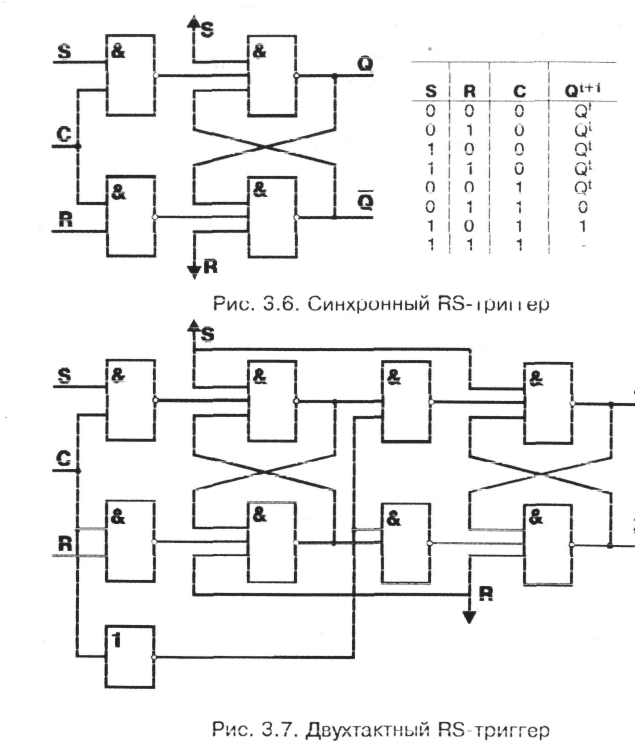

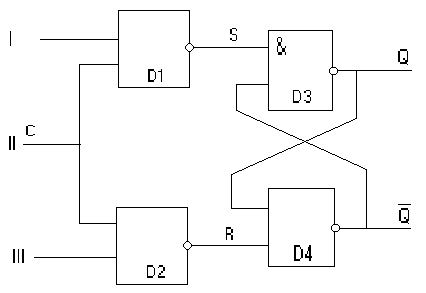

Синхронизируемый однотактный

RS-триггер приведен на рисунке 3.3.1.3. Такие RS-триггеры имеют два

информационных входа R и S и вход синхронизации C. Кроме того, триггер может

иметь несинхронизируемые входы R и S. В этом случае функционирование триггера

осуществляется либо под воздействием несинхронизируемых входов при С=0, либо под

воздействием синхронизируемых входов. В последнем случае на несинхронизируемых

входах должны присутствовать сигналы, которые не влияют на состояние схемы.

На рисунке 3.3.1.4 приведена временная диаграмма

иллюстрирующая работу синхронного однотактного RS-триггера.

В этом случае функционирование триггера

осуществляется либо под воздействием несинхронизируемых входов при С=0, либо под

воздействием синхронизируемых входов. В последнем случае на несинхронизируемых

входах должны присутствовать сигналы, которые не влияют на состояние схемы.

На рисунке 3.3.1.4 приведена временная диаграмма

иллюстрирующая работу синхронного однотактного RS-триггера.

Рисунок 3.3.1.3 — Схема синхронного RS-триггера

Рисунок 3.3.1.4 — Диаграмма работы синхронного RS-триггера

Таблица 3.3.1.2 определяет переходы RS-триггера для синхронизируемых входов R и S. Работа в соответствии с данной таблицей осуществляется при сигнале несинхронизируемого входа R=1 и при С=1.

|

R |

S |

Q |

Примечание |

|

1 |

1 |

Q |

Хранение |

|

1 |

0 |

1 |

Установка 1 |

|

0 |

1 |

0 |

Установка 0 |

|

0 |

0 |

— |

Запрещено |

Таблица 3. 3.1.2 — Таблица

переходов для однотактного RS-триггера

3.1.2 — Таблица

переходов для однотактного RS-триггера

Входная информация заносится в синхронизируемый однотактный RS-триггер через элементы входной логики 1 и 2 в момент поступления сигнала синхронизации С. В отсутствие сигнала синхронизации триггер может быть установлен в состоянии 0 путем подачи на несинхронизируемые вход R сигнала R=0.

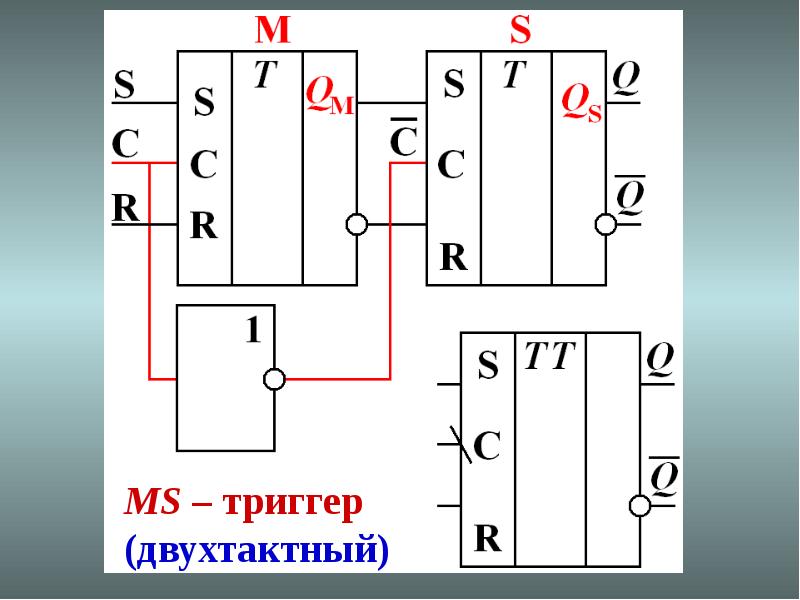

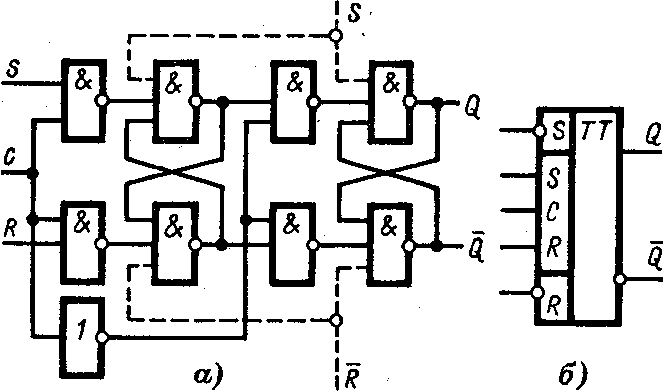

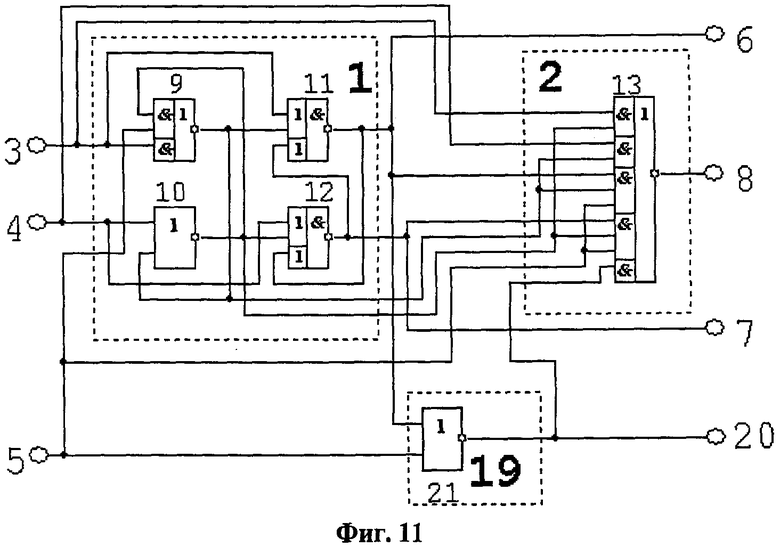

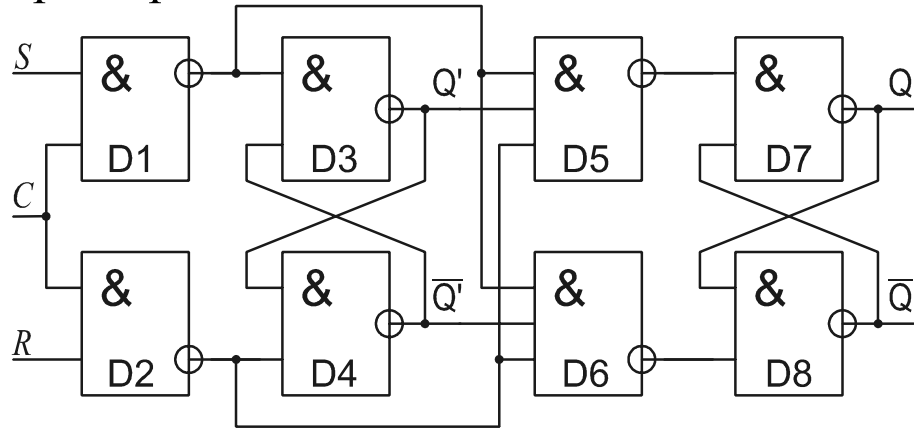

Двухтактный RS-триггер.

Устойчивая работа однотактных RS- триггеров в схеме с передачей информации между

триггерами возможно только в случае, если занесение в триггер информации

осуществляется после завершения передачи информации о прежнем его состоянии в

другой триггер (см. рисунок 3.3.1.5).

Это достаточно просто обеспечивается при использовании двух серий находящихся в

противофазе синхросигналов. Таблица 3.3.1.3 задает закон

функционирования такого двухтактного триггера. Этот тирггер изменяет свои

состояния только после окончания действия сигнала синхронизации С=1 (переход в

режим хранения информации). Поэтому из двухтактных триггеров можно строить

произвольные схемы, в том числе подавать сигналы с выхода триггера на его вход.

Поэтому из двухтактных триггеров можно строить

произвольные схемы, в том числе подавать сигналы с выхода триггера на его вход.

|

R |

S |

Q |

Примечание |

|

0 |

0 |

Q |

Хранение |

|

1 |

0 |

0 |

Установка 0 |

|

0 |

1 |

1 |

Установка1 |

|

1 |

1 |

— |

Запрещено |

Таблица 3. =1, первый RS- триггер перейдет в режим хранения,

а второй примет то же состояние, что и первый. В результате к следующему такту

на входе двухтактного RS- триггера появится сигнал нового состояния. На рисунке 3.3.1.6, приведена временная диаграмма иллюстрирующая

работу двухтактного RS-триггера.

=1, первый RS- триггер перейдет в режим хранения,

а второй примет то же состояние, что и первый. В результате к следующему такту

на входе двухтактного RS- триггера появится сигнал нового состояния. На рисунке 3.3.1.6, приведена временная диаграмма иллюстрирующая

работу двухтактного RS-триггера.

Рисунок 3.3.1.6 — Диаграмма работы двухтактного RS-триггера

Проектирование схем в Electronics Workbench

При проектировании схем в Electronics Workbench использовались элементы панели инструментов «Digital» и соответствующие функциональные элементы : Or, Nor, And, Nand.

Рисунок 3.3.1.7 — Панель инструментов «Digital»

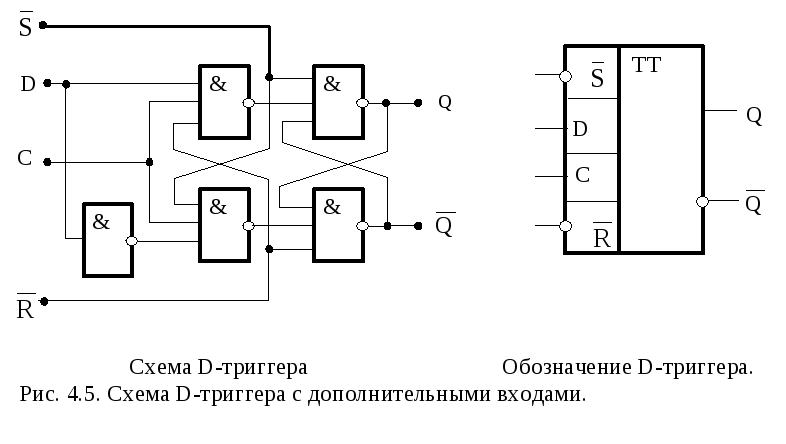

Триггер типа D (от слова delay – задержка)

принимает информацию по одному входу и реализует функцию временной задержки. D-триггер имеет только режимы установки 1 и 0. В связи с этим несинхронизируемый

D-триггер не применяется, т.к. его выход будет просто повторять входной сигнал.

Синхронизируемы однотактный D-триггер задерживает рапространение входного

сигнала на время паузы между синхросигналами (задержка на полпериода). Для

задержки на период (на один такт) используется двухтактный D-триггер.

D-триггер имеет только режимы установки 1 и 0. В связи с этим несинхронизируемый

D-триггер не применяется, т.к. его выход будет просто повторять входной сигнал.

Синхронизируемы однотактный D-триггер задерживает рапространение входного

сигнала на время паузы между синхросигналами (задержка на полпериода). Для

задержки на период (на один такт) используется двухтактный D-триггер.

|

Inputs |

Outputs | |||||

|

D |

C |

S |

R |

Q |

Q^ |

|

|

X |

X |

1 |

0 |

0 |

1 | |

|

X |

X |

0 |

1 |

1 |

0 | |

|

X |

X |

0 |

0 |

1 |

0 | |

|

X |

0 |

1 |

1 |

Q’ |

QB’ | |

|

X |

1 |

1 |

1 |

Q’ |

QB’ | |

|

0 |

RE |

1 |

1 |

0 |

1 | |

|

1 |

RE |

1 |

1 |

1 |

0 | |

Таблица 3. —

инверсный информационный выход

—

инверсный информационный выход

Параметры S и

R служат для задания начальных условий

Триггер типа JK — универсален, с раздельной установкой нулевого и единичного состояния, в зависимости от соединения его входов он может работать как RS, T, D триггера. В отличие от триггера типа RS в нем не запрещена одновременная подача сигналов на оба входа. Входы J и K эквивалентны входам S и R установки триггера соответственно в состояния “1” и “0”.При объединении входов J и K и при подаче на них счетных импульсов.Вход J при раздельном использовании входов играет роль входа установки в единицу, а вход K — роль входа установки в нуль.

Рисунок 3.3.1.9 — Условное обозначение JK-триггера

Параметры синхронного JK-триггера:

C

— синхронизирующий входJ и K — информационные входы триггера

S — установка 1

R — установка 0

Q — информационный выход

Q^ — инверсный информационный выход

Параметры S и R служат для задания начальных условий (см.

X

X

X

1

0

0

1

X

X

X

0

1

1

0

X

X

X

0

0

1

0

X

X

0

1

1

Q’

QB’

X

X

1

1

1

Q’

QB’

0

0

FE

1

1

Q’

QB’

0

1

FE

1

1

0

1

1

0

FE

1

1

1

0

1

1

FE

1

1

QB’

Q’

Таблица 3. 3.1.5 — Таблица

истинности синхронного JK-триггера

3.1.5 — Таблица

истинности синхронного JK-триггера

Триггер типа T называется триггером со счетным входом (или счетным триггером). Он изменяет свое состояние на противоположное каждый раз, когда на его вход приходит очередной сигнал. Обозначение триггера пришло от первой буквы анг.слова toggle-защелка.

Т.к. в Electronics Workbench не приводится T-триггер его можно получить объединив информационные входы JK-триггера.

Задание:

— схемы триггеров;

— временные диаграммы работы триггеров.

Задания выполняются соответственно по вариантам:

- Схема двухтактного RS-триггера на базе элементов ИЛИ-НЕ;

- Схема двухтактного RS-триггера с использованием микросхемы приведенной Electronics Workbench;

- Схема D -триггера с использованием микросхемы приведенной в Electronics Workbench;

- Схема JK-триггера с использованием микросхемы приведенной в Electronics Workbench;

- Схема T-триггера с использованием микросхемы приведенной в Electronics Workbench.

Примечание: Для построения и анализа работы T, D и JK триггеров используйте их условные обозначения.

Вернуться к содержанию

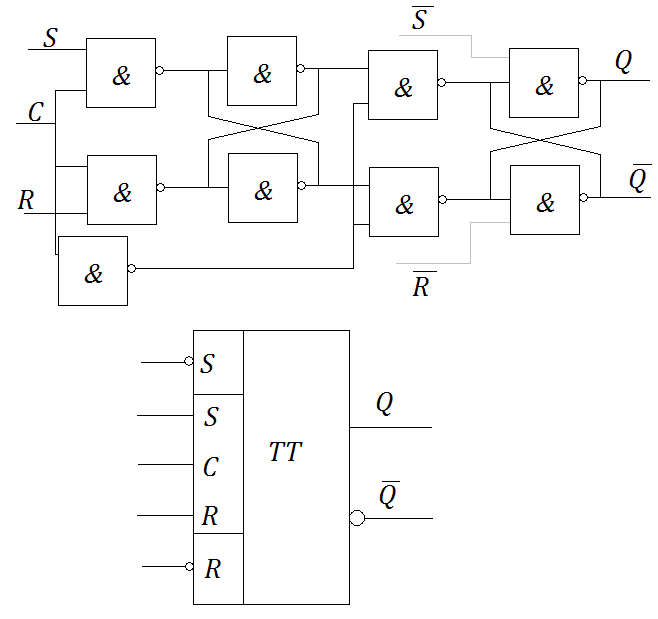

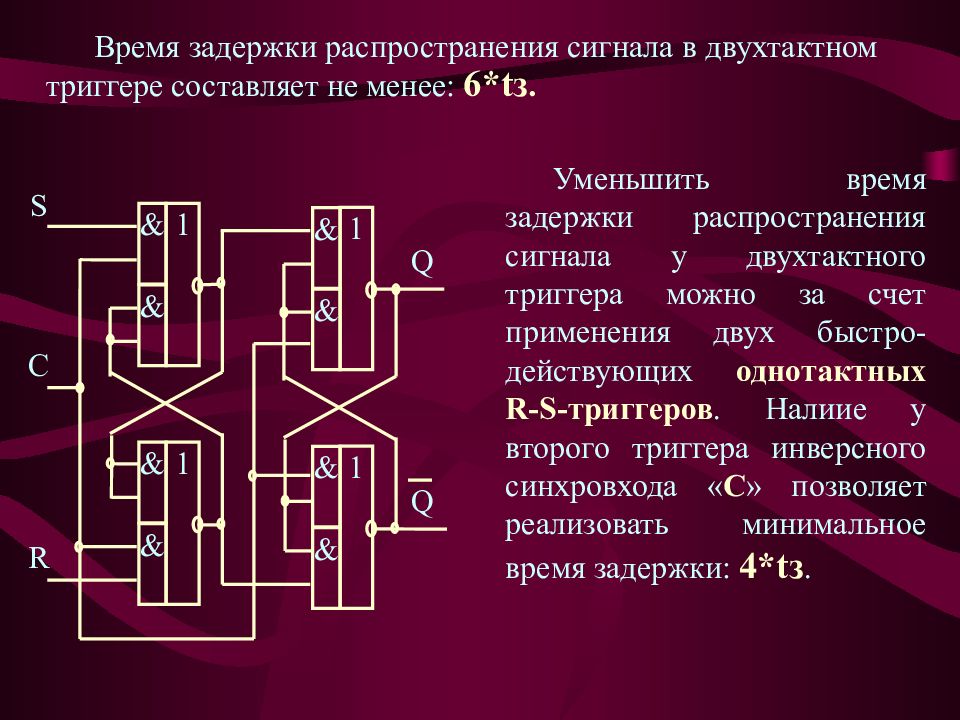

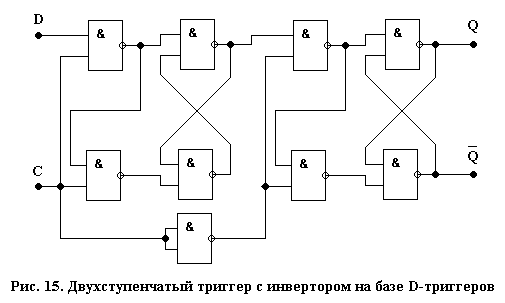

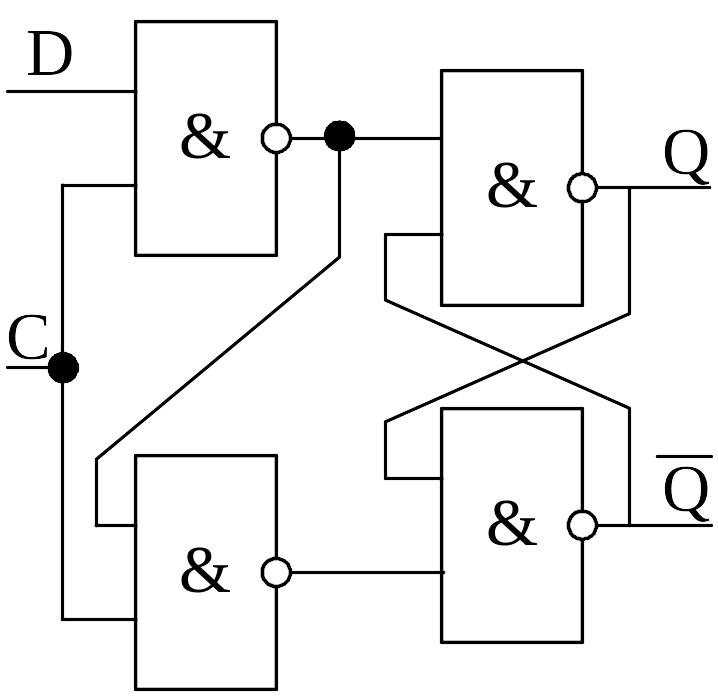

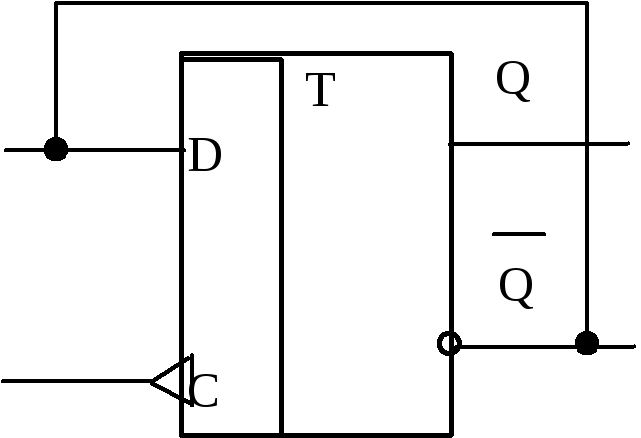

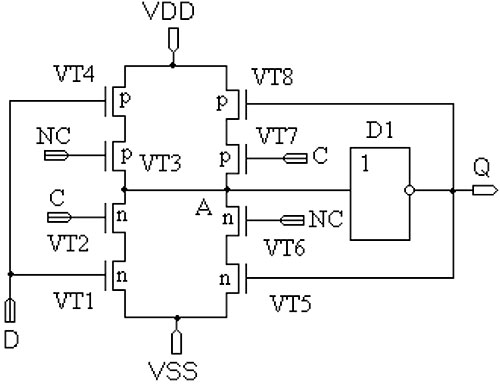

Двухтактный ( двухступенчатый) D-триггер

D — триггер можно выполнить двухступенчатым.

Первая ступень представляет собой одноступенчатый D-триггер, а вторая — синхронный RS-триггер.

На схемах двухтактный D- триггер обозначается следующим образом.

Рис. 0.21

Принцип действия двухтактного D- триггера основан на принципе действия RS триггера с динамическими входами. Т.е. первая ступень переключается по переднему фронту тактового импульса, вторая по его срезу.

Схема двухтактного D- триггера имеет следующий вид.

Рис. 0.22

Работа двухтактного D- триггера наглядно отражена в описании его принципа работы

Так же как и в одноступенчатом D-триггере в 2-х ступенчатой схеме возможно реализовать функцию valve. В результате получим универсальный 2-х ступенчатый DV-триггер.

Рис. 0.23

Условное обозначение такого триггера имеет следующий вид:

Рис. 0.24

Двухступенчатый D-триггер получил широкое применение из-за его универсальности. Так, например, если соединить с D входом, то с каждым синхроимпульсом будет меняться потенциал на входе D и, следовательно, состояние триггера. Таким образом, получается счетный Т-триггер.

Таким образом, получается счетный Т-триггер.

Рис. 0.25

Кроме того, на базе таких триггеров можно реализовать и другие виды триггеров.

Развитие универсальных триггеров происходит в связи с необходимостью экономии средств при проектировании и изготовлении радиоэлектронной аппаратуры.

Реальные микросхемы функционально являющиеся D -триггерами обозначаются следующим образом: ТМ. Так, например, микросхема 155ТМ2 является D-триггером.

Итак D-триггеры, цифровые устройства со счётным запуском, и не имеющие запрещённых комбинаций сигналов, подаваемых на их информационные входы.

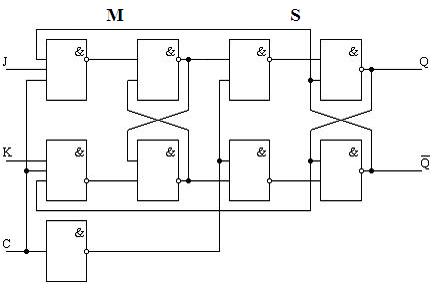

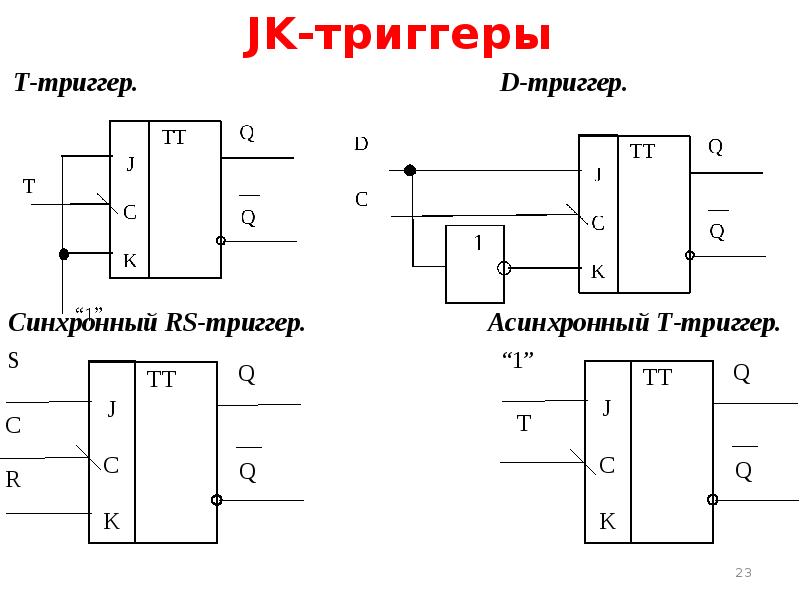

JK-триггеры.

JK-триггер –это триггер с двумя сигнальными и одним синхронным входами.

Такие триггеры часто называются универсальными, так как на их основе можно получить RS- и T-триггеры.

Название выводов у таких триггеров пошло от английских слов jerh -резкий толчок, kill — убить

Назначение- JK-триггеров универсальное.

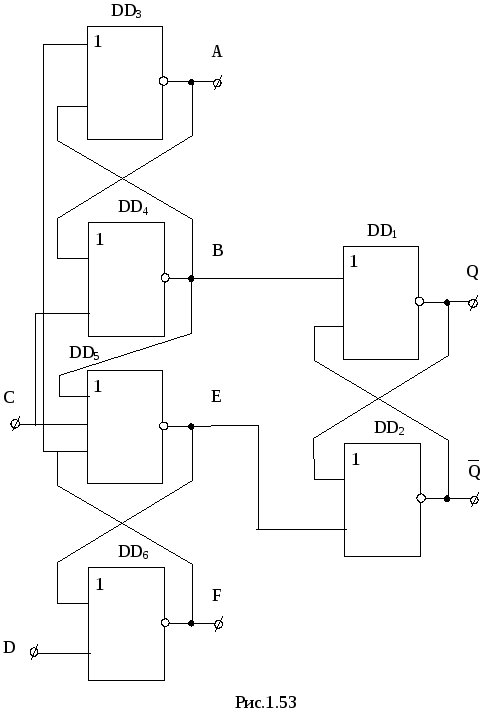

Выполняется JK-триггер по двухступенчатой схеме с использованием основного и вспомогательного RS-триггера соединённых последовательно и имеющих обратную связь..

JK-триггеры получили следующее условное обозначение:

Рис. 0.26

Микросхемы JK-триггеров имеют обозначение ТВ. Например JK-триггер исполненный в комплекте микросхем 555 серии имеет обозначение — 555ТВ9.

Информационные входы J и K аналогичны входам S и R тактируемого RSC- триггера.

Принцип действия JK-триггеров аналогичен RSC триггеру, но JK-триггеры не имеют запрещающей комбинации. Т.е. во время действия тактового импульса сигнал записывается в основной триггер, а в момент окончания сигнал считывается вспомогательным RS-триггером.

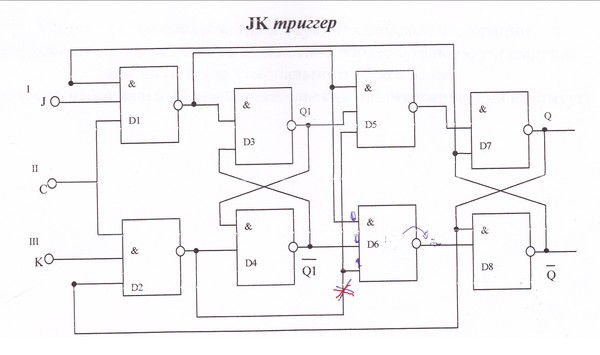

Схема JK-триггеров.

Рис. 0.27

На схеме, представленной выше, входы J, K являются информационными входами. Они аналогичны S и R входам тактируемого RSC-триггера (R эквивалентен K входу, S — J входу).

Работу (изменение состояний) JK — триггера при С=1 можно представить в виде следующей таблицы.

| Jn | Kn | Qn+1 |

| Qn | ||

При J=1, К=0 по срезу тактового импульса триггер устанавливается в единичное состояние, т.е. Q=1.

При J=0, К=1 — переключается в нулевое состояние, т.е. Q=0.

При J=0, К=0 — хранит раннее записанную информацию.

В данном триггере так же возможно осуществление счётного режима. Сказанное происходит при J=К=1. Триггер переключается каждым счетным импульсом приходящим на вход С..

Рассмотрим работу JK — триггера более подробно.

При J=K=0 на выходах DD1 и DD2 устанавливаются 1, которые для триггеров с инверсными входами являются пассивными сигналами. Следовательно, триггер Т1 и JK — триггер в целом своего состояния не изменяет.

Следовательно, триггер Т1 и JK — триггер в целом своего состояния не изменяет.

Чтобы на выходе DD1 появился 0, необходимо чтобы J=1, C=1, =1. Тогда триггер Т1 переходит в 1 состояние, а по срезу тактового импульса и триггер Т2 переходит в 1. Следовательно, Q2=1.

При К=1, С=1, Q=1 на выходе DD2 появляется 0, переводящая триггер Т1 в нулевое состояние, а по срезу триггер Т2 в 0 и, следовательно, JK — триггер в целом переходит в нулевое состояние (Q=0, =1).

В отличие от RSC — триггеров одновременное присутствие единицы на сигнальных входах JK не является запрещающей комбинацией. При этом JK — триггер работает в счетном режиме, т.е. переключается спадом каждого тактирующего импульса.

На базе JК — триггеров можно построить любой из ранее рассмотренных.

Узнать еще:

Справочник «Цифровые Интегральные Микросхемы»

Справочник «Цифровые Интегральные Микросхемы» [ Содержание ]2.5.

3. JK-триггеры

3. JK-триггерыJK-триггеры подразделяются на универсальные и комбинированные. Универсальный JK-триггер имеет два информационных входа J и K. По входу J триггер устанавливается в состояние Q=1, /Q=0, а по входу K-в состояние Q=0, /Q=1.

JK-триггер отличается от RS-триггера прежде всего тем что в нем устранена неопределенность, которая возникает в RS-триггере при определенной комбинации входных сигналов.

Универсальность JK-триггера состоит в том, что он может выполнять функции RS-, Т- и D-триггеров.

Комбинированный JK-триггер отличается от универсального наличием дополнительных асинхронных входов S и R для предварительной установки триггера в определенное состояние (логической 1 или 0).

Простейший JK-триггер можно получить из синхронного RS-триггера с динамическим управлением, если ввести дополнительные обратные связи с выходов триггера на входы, которые позволяют устранить неопределенность в таблице состояний (рис. 2.50.а).

Рис.

2.50.a. Преобразование синхронного RS-триггера в JK-триггер;

2.50.a. Преобразование синхронного RS-триггера в JK-триггер;Если на входы J и К подать уровень логической единицы, то получим T-триггер, который переключается каждым входным импульсом (рис. 2.50, б).

Рис. 2.50.б. Преобразование JK-триггера в T-триггер;

На рис. 2.50.в приведено условное обозначение JK-триггера и таблица состояний. При входных сигналах J=К=0 состояние триггера не изменяется, так как напряжение низкого уровня на одном входе элемента И-НЕ отменяет пpохождение сигналов от других его входов и удерживает выходной сигнал в текущем логическом состоянии.

Рис. 2.50.в. условное обозначение JK-триггера

| Установлено | Записано | ||

|---|---|---|---|

| J | K | Qn+1 | /Qn+1 |

| H | H | Без изменений Qn /Qn | |

| Н | В | Н=0 | В=1 |

| В | Н | В=1 | Н=0 |

| В | В | Переброс /Qn Qn | |

Если на входы J и К подать взаимно противоположные уровни,

то при подаче перепада напряжения на вход С выходы JK-триггера

устанавливаются в такие же состояния. При подаче на входы J и К

одновременно напряжений высокого уровня триггер переключается в состояние,

противоположное предыдущему, если на вход синхронизации С подать

перепад напряжения.

При подаче на входы J и К

одновременно напряжений высокого уровня триггер переключается в состояние,

противоположное предыдущему, если на вход синхронизации С подать

перепад напряжения.

Управление полным тактовым импульсом, подаваемым на вход С, применяется для двухступенчатых триггеров (рис. 2.50.г).

Рис. 2.50.г. двухступенчатый JK-триггер;

Такой триггер тоже имеет обратные связи с выходов на входы, исключающие неопределенное состояние триггера.

Рис. 2.50.д. двухступенчатый JK-триггер на логических элементах И-НЕ

с симметричной схемой управления триггера второй ступени;

Из JK-триггера можно получить D-триггер, если вход К соединить со входом J через дополнительный инвертор (рис. 2.50,д).

Рис. 2.50.е. Схема преобразования JK-триггера в D-триггер

Микросхема TB1 (рис. 2.51) представляет собой универсальный двухступенчатый JK-триггер.

Рис. 2.51. Комбинированный JK-триггер — структура микросхемы, условное обозначение и цоколевка микросхемы ТВ1.

Триггер имеет инверсные асинхронные входы установки /S и сброса /R, т. е. с активным низким уровнем. Если на эти входы подать противоположные уровни (низкий — 0 и высокий — 1), то входы J, K и С не действуют и состояния выходов Q и /Q триггера определяются сигналами на входах /S и /R, таблица состояний (табл. 2.27).

| Режим работы | Входы | Выходы | |||||

|---|---|---|---|---|---|---|---|

| /S | /R | J | K | C | Qn+1 | /Qn+1 | |

| Асинхронная установка | 0 | 1 | Х | Х | Х | 1 | 0 |

| Асинхронный сброс | 1 | 0 | Х | Х | Х | 0 | 1 |

| Неопределенность | 0 | 0 | Х | Х | Х | X | X |

| Загрузка «1» (установка) | 1 | 1 | 1 | 0 | _/\_ | 1 | 0 |

| Загрузка «0» (сброс) | 1 | 1 | 0 | 1 | _/\_ | 0 | 1 |

| Переключение | 1 | 1 | 1 | 1 | _/\_ | /Qn | Qn |

| Хранение (нет изменений) | 1 | 1 | 0 | 0 | _/\_ | Qn | /Qn |

Когда на входы /S и /R поданы напряжения высокого уровня,

в триггер можно загружать информацию от входов J и K или

хранить ее (см. таблицу состояний). Каждый из входов J и K

снабжен логическим элементом 3И, т.е. микросхема ТВ1 имеет

три входа J и три входа K. Вход синхронизации C инверсный

динамический. Состояния двухступенчатого триггера переключаются

фронтом и спадом положительного импульса, подаваемого на вход

синхронизации C. Информация со входов J и K загружается в

триггер первой ступени (элементы DD1.3 и DD1.4), когда напряжение

входа C изменяется от низкого уровня к высокому (по фронту) и

переносится в триггер второй ступени по отрицательному перепаду

импульса синхронизации (по спаду). Сигналы на входах J и K не должны

изменяться, если на входе /C присутствует напряжение высокого уровня.

Состояния выходов Q и /Q будут неопределенные, если на входы /S и /R

одновременно подать напряжение низкого уровня, т. е. комбинация

сигналов /S=/R=0 является запрещенной.

таблицу состояний). Каждый из входов J и K

снабжен логическим элементом 3И, т.е. микросхема ТВ1 имеет

три входа J и три входа K. Вход синхронизации C инверсный

динамический. Состояния двухступенчатого триггера переключаются

фронтом и спадом положительного импульса, подаваемого на вход

синхронизации C. Информация со входов J и K загружается в

триггер первой ступени (элементы DD1.3 и DD1.4), когда напряжение

входа C изменяется от низкого уровня к высокому (по фронту) и

переносится в триггер второй ступени по отрицательному перепаду

импульса синхронизации (по спаду). Сигналы на входах J и K не должны

изменяться, если на входе /C присутствует напряжение высокого уровня.

Состояния выходов Q и /Q будут неопределенные, если на входы /S и /R

одновременно подать напряжение низкого уровня, т. е. комбинация

сигналов /S=/R=0 является запрещенной.

Микросхемы ТВ6 и ТВ9, ТВ10 и TB11 содержат по два JK-триггера с общим выводом питания (рис. 2.52).

Рис. 2.52. Структура, условное обозначение и цоколевка микросхем ТВ6, ТВ9;

Рис.

2.52a. Структура, условное обозначение и цоколевка микросхемы ТВ10;

2.52a. Структура, условное обозначение и цоколевка микросхемы ТВ10;Вход синхронизации С у всех триггеров инверсный динамический, поэтому данные от входов J и К переносятся на выходы Q и /Q по отрицательному перепаду импульса С. Когда импульс на входе С переходит от высокого уровня к низкому, сигналы на входах J и К не должны изменяться. Информацию от входов J и К следует загружать в триггер, когда на входе С присутствует напряжение высокого уровня.

У триггеров микросхемы ТВ6 нет входа предварительной установки /S, поэтому в таблице состояний (комбинированного JK-триггера) необходимо исключить первую строку (асинхронную установку 1). Если на вход /R будет подано напряжение низкого уровня, то входы J, К и С не действуют.

У триггеров микросхемы ТВ10 нет входа предварительного сброса /R, поэтому в таблице состояний комбинированного JK-триггера необходимо исключить вторую строку (асинхронный сброс 0).

Для микросхем ТВ6 и ТВ10 в таблице состояний не имеет смысла и

третья строка, т. к, они имеют только по одному асинхронному

входу (либо /S, либо /R). Триггеры микросхемы ТВ11 в отличие

от триггеров микросхемы ТВ9 имеют две общие цепи управления:

вход синхронизации /С и асинхронный вход сброса /R (рис. 2.53).

к, они имеют только по одному асинхронному

входу (либо /S, либо /R). Триггеры микросхемы ТВ11 в отличие

от триггеров микросхемы ТВ9 имеют две общие цепи управления:

вход синхронизации /С и асинхронный вход сброса /R (рис. 2.53).

Рис. 2.53. Условное обозначение и цоколевка микросхемы ТВ11

Микросхемы ТВ14 и ТВ15 содержат по два комбинированных JK-триггера, которые запускаются положительным перепадом импульса синхронизации, т. е. вход С прямой динамический. Отличительной особенностью триггеров данных микросхем является то, что второй информационный вход /К — инверсный, поэтому очень легко такие JK-триггеры превращать в D-триггеры (рис. 2.54).

Рис. 2.54. Структура ТВ15, условные обозначения и цоколевки ТВ14 и ТВ15

Состояние таких триггеров приведено в табл. 2.28.

| Режим работы | Входы | Выходы | |||||

|---|---|---|---|---|---|---|---|

| /S | /R | J | /K | C | Qn+1 | /Qn+1 | |

| Асинхронная установка | 0 | 1 | X | X | X | 1 | 0 |

| Асинхронный сброс | 1 | 0 | X | X | X | 0 | 1 |

| Неопределенность | 0 | 0 | X | X | X | 1 | 1 |

| Загрузка «1» (установка) | 1 | 1 | 1 | 0 | _/\_ | 1 | 0 |

| Загрузка «0» (сброс) | 1 | 1 | 0 | 1 | _/\_ | 0 | 1 |

| Переключение | 1 | 1 | 1 | 0 | _/\_ | /Qn=1 | Qn=0 |

| Хранение (нет изменений) | 1 | 1 | 0 | 1 | _/\_ | 1 | 0 |

Основные параметры триггеров ТТЛ приведены в табл. 2.20.

2.20.

Справочник «Цифровые Интегральные Микросхемы»

Справочник «Цифровые Интегральные Микросхемы» [ Содержание ]2.5.2. D-триггеры

D-триггером называется триггер с одним информационным

входом, работающий так, что сигнал на выходе после

переключения равен сигналу на входе D до переключения,

т. е. Qn+1=Dn Основное назначение D-триггеров — задержка

сигнала, поданного на вход D. Он имеет информационный

вход D (вход данных) и вход синхронизации С. Вход

синхронизации С может быть статическим (потенциальным)

и динамическим. У триггеров со статическим входом С информация

записывается в течение времени, при котором уровень сигнала C=1.

В триггерах с динамическим входом С информация записывается

только в течение перепада напряжения на входе С. Динамический

вход изображают на схемах треугольником. Если вершина треугольника

обращена в сторону микросхемы (прямой динамический вход), то

триггер срабатывает по фронту входного импульса, если от нее

(инверсный динамический вход) — по срезу импульса. В таком

триггере информация на выходе может быть задержана на один такт

по отношению к входной информации.

В таком

триггере информация на выходе может быть задержана на один такт

по отношению к входной информации.

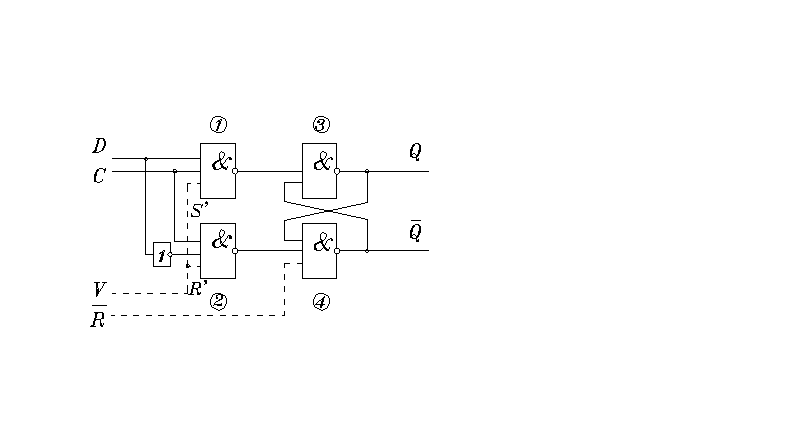

D-триггеры могут быть построены по различным схемам. На рис. 2.43,а показана схема одноступенчатого D-триггера на элементах И-НЕ и его условное обозначение. Триггер имеет прямые статические входы (управляющий сигнал — уровень логической единицы). На элементах DD1.1 и DD1.2 выполнена схема управления, а на элементах DD1.3 и DD1.4 асинхронный RS-триггер.

Рис. 2.43. Синхронный D-триггер: а — схема D-триггера на элементах И-НЕ и условное обозначение;

б — временные диаграммы; в — преобразование синхронного RS-триггера в синхронный D-триггер;

г — временные диаграммы записи и считывания.

Если уровень сигнала на входе С = 0, состояние триггера устойчиво и не зависит от уровня сигнала на информационном входе D. При этом на входы асинхронного RS-триггера с инверсными входами (DD1.3 и DD1.4) поступают пассивные уровни /S = /R = 1.

При подаче на вход синхронизации уровня С = 1 информация на

прямом выходе будет повторять информацию, подаваемую на вход D.

Следовательно, при C=0 Qn+1=Qn, а при C=l Qn+1=Dn. Временные диаграммы, поясняющие работу D-триггера, приведены на рис. 2.43,б.

D-триггер возможно получить из синхронного RS-триггера, если ввести дополнительный инвертор DD1.1 между входами S и R (рис. 2.43,в). В таком триггере состояние неопределенности для входов S и R исключается, так как инвертор DD1.1 формирует на входе R сигнал /S. Временные диаграммы записи в D-триггер напряжений высокого и низкого входных уровней и их считывание приведены на рис. 2.43,г. Обязательным условием правильной работы D-триггера является наличие защитного временного интервала после прихода импульса на вход D перед тактовым импульсом (вход С). Этот интервал времени tn+1-tn зависит от справочных данных на D-триггер.

Комбинированные D-триггеры имеют дополнительные входы

асинхронной установки логических 0 и 1 — входы S и R.

Схема и условное обозначение одного такого триггера

представлены на рис. 2.44. Триггер собран на шести

элементах И-НЕ по схеме трех RS-триггеров. Входы /S и /R служат

для первоначальной установки триггера в определенное состояние.

Входы /S и /R служат

для первоначальной установки триггера в определенное состояние.

Рис. 2.44. Комбинированный D-триггер и его условное обозначение.

Если C=D=0, установить /S=0, а /R=1, то элементы DD1.1 … DD1.5 будут закрыты, а элемент DD1.6 будет открыт, т. е. Q=l, /Q=0. При снятии нулевого сигнала со входа /S, откроется элемент DD1.1, состояние остальных элементов не изменится. При подаче единичного сигнала на вход С на всех входах элемента DD1.3 будут действовать единичные сигналы и он откроется, а элемент DD1.6 закроется: /Q = 1. Теперь на всех входах элемента DD1.5 действуют единичные сигналы и он будет открыт: Q = 0. Следовательно, после переключения триггера сигнал на выходе Q стал равным сигналу на входе D до переключения: Qn+1=Dn=0. После снятия единичного сигнала со входа С состояние триггера не изменится.

D-триггер с динамическим входом C может работать как T-триггер.

Для этого необходимо вход С соединить с инверсным выходом триггера /Q

(рис. 2.45,а). Если на входе D поставить дополнительный двухвходовый

элемент И и инверсный выход триггера /Q соединить с одним из входов

элемента И, а на второй вход подать сигнал EI, то получим T-триггер с

дополнительным разрешением по входу (рис. 2.45,б).

2.45,а). Если на входе D поставить дополнительный двухвходовый

элемент И и инверсный выход триггера /Q соединить с одним из входов

элемента И, а на второй вход подать сигнал EI, то получим T-триггер с

дополнительным разрешением по входу (рис. 2.45,б).

Рис. 2.45. Схемы преобразования D-триггера. а — преобразование D-триггера в T-триггер и его временная диаграмма работы;

б — преобразование D-триггера в в T-триггер с дополнительным входом расширения EI и его временная диаграмма работы;

Микросхема ТМ2 содержит два независимых комбинированных D-триггера,

имеющих общую цепь питания. У каждого триггера имеется один

информационный вход D, вход синхронизации С и два дополнительных

входа /S и /R независимой асинхронной установки триггера в единичное

и нулевое состояния, а также комплементарные выходы Q и /Q (рис. 2.46).

Логическая структура одного D-триггера (рис. 2.46) содержит следующие

элементы: основной асинхронный RS-триггер (ТЗ), вспомогательный

синхронный RS-триггер (Т1) записи логической единицы (высокого уровня)

в основной триггер, вспомогательный синхронный RS-триггер (Т2) записи

логического нуля (низкого уровня) в основной триггер. Входы /S и /R — асинхронные, потому что они работают (сбрасывают состояние

триггера) независимо от сигнала на тактовом входе, активный уровень

для них низкий (т. е. инверсные входы /S и /R).

Входы /S и /R — асинхронные, потому что они работают (сбрасывают состояние

триггера) независимо от сигнала на тактовом входе, активный уровень

для них низкий (т. е. инверсные входы /S и /R).

Рис. 2.46. Структура D-триггера микросхемы ТМ2

Асинхронная установка D-триггера в единичное или нулевое состояния осуществляется подачей взаимопротивоположных логических сигналов на входы /S и /R. В это время входы D и С не влияют.

Если на входы /S и /R одновременно подать сигнал низкого уровня (логический нуль), то на обоих выходах триггера Q и /Q будет высокий уровень (логическая единица). Однако после снятия этих сигналов со входов /S и /R состояние триггера будет неопределенным. Поэтому комбинация /S=/R=0 для этих входов является запрещенной.

Загрузить в триггер входные уровни В или Н (т. е. логические 1 или 0) можно,

если на входы /S и /R подать напряжение высокого уровня: /S=/R=1. Сигнал от

входа D передается на выходы триггера при поступлении положительного перепада

импульса на вход С (изменение от низкого* к высокому). Однако, чтобы D-триггер

переключался правильно (согласно таблице состояний, табл. 2.24), необходимо

уровень на входе D зафиксировать заранее, т. е. до прихода перепада на вход С.

Причем этот защитный временной интервал должен быть больше времени задержки

распространения сигнала в триггере (определяется по справочнику).

Однако, чтобы D-триггер

переключался правильно (согласно таблице состояний, табл. 2.24), необходимо

уровень на входе D зафиксировать заранее, т. е. до прихода перепада на вход С.

Причем этот защитный временной интервал должен быть больше времени задержки

распространения сигнала в триггере (определяется по справочнику).

| Режим работы | Входы | Выходы | ||||

|---|---|---|---|---|---|---|

| /S | /R | D | C | Q | /Q | |

| Асинхронная установка | 0 | 1 | X | X | 1 | 0 |

| Асинхронный сброс | 1 | 0 | Х | Х | 0 | 1 |

| неопределенность | 0 | 0 | Х | Х | 1 | 1 |

| Загрузка «1» (установка) | 1 | 1 | 1 | _/ | 1 | 0 |

| Загрузка «0» (сброс) | 1 | 1 | 0 | _/ | 0 | 1 |

Цоколевка микросхемы ТМ2 приведена на рис. 2.47,

а основные параметры см. в табл. 2.20а.

2.47,

а основные параметры см. в табл. 2.20а.

Рис. 2.47. Условное обозначение и

цоколевка микросхемы ТМ2

Микросхемы ТM5 и ТМ7 содержат по четыре D-триггера, входы синхронизации

которых попарно соединены и обозначены как входы разрешения загрузки EI.

Если на такой вход разрешения EI подается напряжение высокого уровня,

то информация, поступающая на входы D, передается на выходы триггеров.

При напряжении низкого уровня на входе разрешения EI на выходах триггеров

сохраняются предыдущие состояния (состояние входов D безразлично).

В триггерах будет зафиксирована информация, имевшаяся на входах D, если

состояние входа EI переключить от напряжения высокого уровня к низкому.

Такие триггеры используются в качестве четырехразрядного регистра

хранения информации с непарным тактированием разрядов, а также в

качестве буферной памяти и элемента задержки. Каждый триггер микросхемы

ТМ5 имеет только прямой выход Q, а каждый триггер микросхемы ТМ7 имеет

прямые Q и инверсные /Q выходы. Функциональные схемы, цоколевка,

схема одного D-триггера и временные диаграммы работы приведены

на рис. 2.48, а, основные параметры триггеров даны в

табл. 2.20, состояния триггеров даны в

табл. 2.25.

Функциональные схемы, цоколевка,

схема одного D-триггера и временные диаграммы работы приведены

на рис. 2.48, а, основные параметры триггеров даны в

табл. 2.20, состояния триггеров даны в

табл. 2.25.

Рис. 2.48. Функциональные схемы, цоколевки, структура D-триггера и временные диаграммы микросхем ТМ5, ТМ7.

| Режим работы | Входы | Выходы | ||

|---|---|---|---|---|

| EI | D | Qn+1 | /Qn+1 | |

| Разрешение передачи данных на выход | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 | |

| Защелкивание данных | 0 | Х | Qn=1 | /Qn=0 |

Микросхемы. TM8 и ТМ9 содержат четыре и шесть D-триггеров соответственно. Они имеют общие входы синхронного сброса /R (установки в состояние низкого уровня)

и входа синхронизации C. Структура ТМ8 и ТМ и их цоколевка приведены на рис. 2.49.

Они имеют общие входы синхронного сброса /R (установки в состояние низкого уровня)

и входа синхронизации C. Структура ТМ8 и ТМ и их цоколевка приведены на рис. 2.49.

Рис. 2.48. Функциональные схемы и цоколевки микросхем ТМ8 и ТМ9.

Триггеры микросхемы ТМ9 имеют только прямые входы Q, а триггеры ТМ8 — прямые и инверсные выходы Q и /Q. На входах C и /R поставлены дополнительные инверторы. Микросхемы К1533ТМ8, К1533ТМ9 имеют повышенную нагрузочную способность, т.е. на каждом из выходов поставлены дополнительные инверторы. Функционрированне триггеров в микросхемах ТМ8 и ТМ9 соответствует таблице состояний (табл. 2.26).

| Режим работы | Входы | Выходы | |||

|---|---|---|---|---|---|

| /R | D | C | Qn+1 | /Qn+1 | |

| Сброс | 0 | X | X | 0 | 1 |

| Загрузка «1» | 1 | 1 | _/ | 1 | 0 |

| Загрузка «0» | 1 | 0 | _/ | 0 | 1 |

Установка всех триггеров в состояние Q = 0 произойдет, когда на

асинхронный вход /R подать напряжение низкого уровня — 0. Входы С и D в это время не действуют. Информацию от входов D можно

загрузить в триггеры, если на вход /R подать напряжение высокого

уровня — 1. Тогда при подаче на вход синхронизации С положительного

перепада напряжения (фронта импульса) и предварительно поданного

на вход D напряжения высокого или низкого уровня появится на

выходе Q высокий или низкий уровень.

Входы С и D в это время не действуют. Информацию от входов D можно

загрузить в триггеры, если на вход /R подать напряжение высокого

уровня — 1. Тогда при подаче на вход синхронизации С положительного

перепада напряжения (фронта импульса) и предварительно поданного

на вход D напряжения высокого или низкого уровня появится на

выходе Q высокий или низкий уровень.

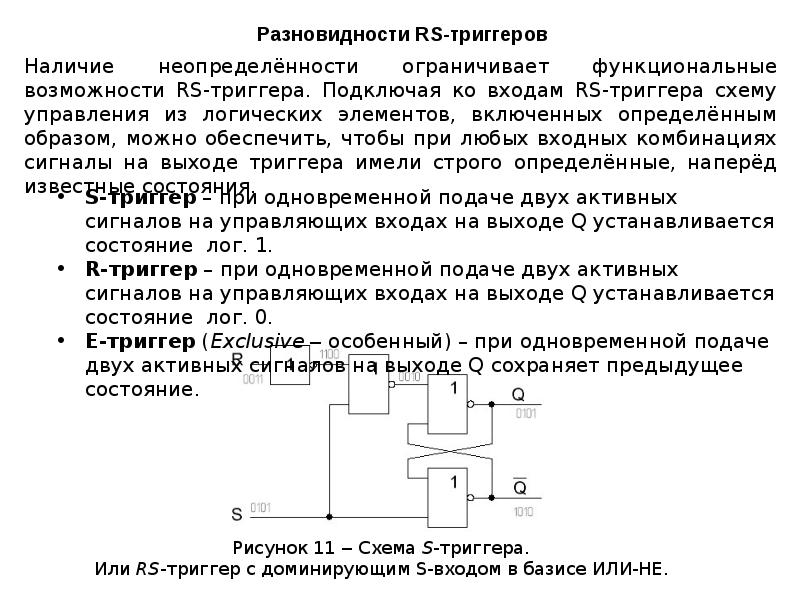

RS-триггер. Принцип работы и его типовая схема на логических элементах.

Устройство и принцип работы RS-триггера

Одним из важнейших элементов цифровой техники является триггер (англ. Trigger — защёлка, спусковой крючок).

Сам триггер не является базовым элементом, так как он собирается из более простых логических схем. Семейство триггеров весьма обширно. Это триггеры: T, D, C, JK, но основой всех является самый простой RS-триггер.

Без RS триггеров невозможно было бы создание никаких вычислительных устройств от игровой приставки до суперкомпьютера. У триггера два входа S (set) — установка и R (reset) — сброс и два выхода Q-прямой и Q— инверсный. Инверсный выход имеет сверху чёрточку. Триггер бистабильная система, которая может находиться в одном из двух устойчивых состояний сколь угодно долго. На рисунке показан RS-триггер выполненный на элементах 2ИЛИ – НЕ.

Инверсный выход имеет сверху чёрточку. Триггер бистабильная система, которая может находиться в одном из двух устойчивых состояний сколь угодно долго. На рисунке показан RS-триггер выполненный на элементах 2ИЛИ – НЕ.

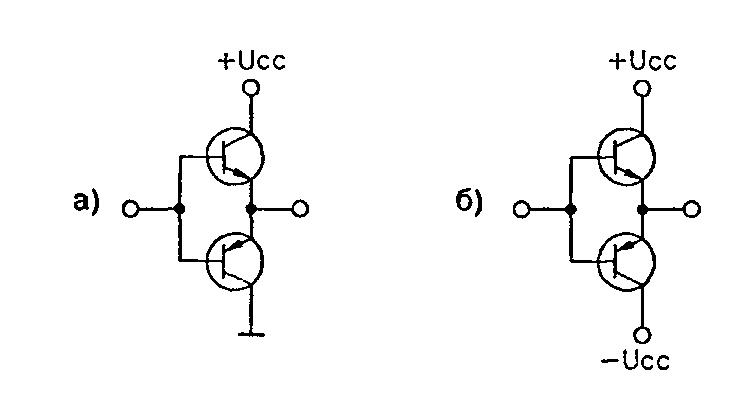

Точно так же триггер может быть выполнен и на элементах 2И – НЕ.

Единственная разница это то, что триггер на элементах И – НЕ активируется, то есть переводится в другое состояние потенциалом логического нуля. Триггер, собранный на элементах ИЛИ – НЕ активируется логической единицей. Это определяется таблицей истинности логических элементов. При подаче положительного потенциала на вход S мы получим на выходе Q высокий потенциал, а на выходе Q низкий потенциал. Тем самым мы записали в триггер, как в ячейку памяти, единицу. Пока на вход R не будет подан высокий потенциал, состояние триггера не изменится.

На принципиальных схемах триггер изображается следующим образом.

Два входа R и S, два выхода прямой и инверсный и буква Т означающая триггер.

Хорошо отображает принцип работы RS-триггера несложная схема, собранная на двух элементах 2И – НЕ. Для этого используется микросхема 155ЛА3, которая содержит четыре таких элемента. Нумерация на схеме соответствует выводам микросхемы. Напряжение питания +5V подаётся на 14 вывод, а минус подаётся на 7 вывод микросхемы. После включения питания триггер установится в одно из двух устойчивых состояний.

Исходя из того, что сопротивление переходов транзисторов логических элементов не может быть абсолютно одинаковым, то триггер после включения питания, как правило, принимает одно и то же состояние.

Допустим, после подачи питания у нас горит верхний по схеме светодиод HL1. Можно сколько угодно нажимать кнопку SB1 ситуация не изменится, но достаточно на долю секунды замкнуть контакты кнопки SB2 как триггер поменяет своё состояние на противоположное. Горевший светодиод HL1 погаснет и загорится другой — HL2. Тем самым мы перевели триггер в другое устойчивое состояние.

На данной схеме всё достаточно условно, а на реальном триггере принято считать, что если на прямом выходе «Q» высокий уровень то триггер установлен, если уровень низкий то триггер сброшен.

Основной недостаток рассматриваемого триггера это, то, что он асинхронный. Другие более сложные схемы триггеров синхронизируются тактовыми импульсами общими для всей схемы и вырабатываемые тактовым генератором. Кроме того сложная входная логика позволяет держать триггер в установленном состоянии до тех пор пока не будет сформирован сигнал разрешения смены состояния триггера.

RS-триггер может быть и синхронным, но двух логических элементов для этого мало.

На рисунке изображена схема синхронного RS-триггера. Такой триггер может быть собран на микросхеме К155ЛА3, которая содержит как раз четыре элемента 2И – НЕ. В данной схеме переключение триггера из одного состояния в другое может быть осуществлено только в момент прихода синхроимпульса на вход «C«.

На рассмотренной выше схеме переключение триггера осуществляется с помощью кнопок. Такой вариант используется достаточно часто и именно для кнопочного управления какой-либо аппаратурой. В электронике существует понятие «дребезг контактов» то есть, когда мы нажимаем кнопку, на вход устройства проникает целый пакет импульсов, который может привести к серьёзным нарушениям в работе. Использование RS-триггера позволяет избежать этого.

Использование RS-триггера позволяет избежать этого.

Благодаря своей простоте и недорогой стоимости RS-триггеры широко применяются в схемах индикации. Часто для повышения надёжности и устранения возможности случайного срабатывания RS-триггер собирается по так называемой двухступенчатой схеме. Вот схема.

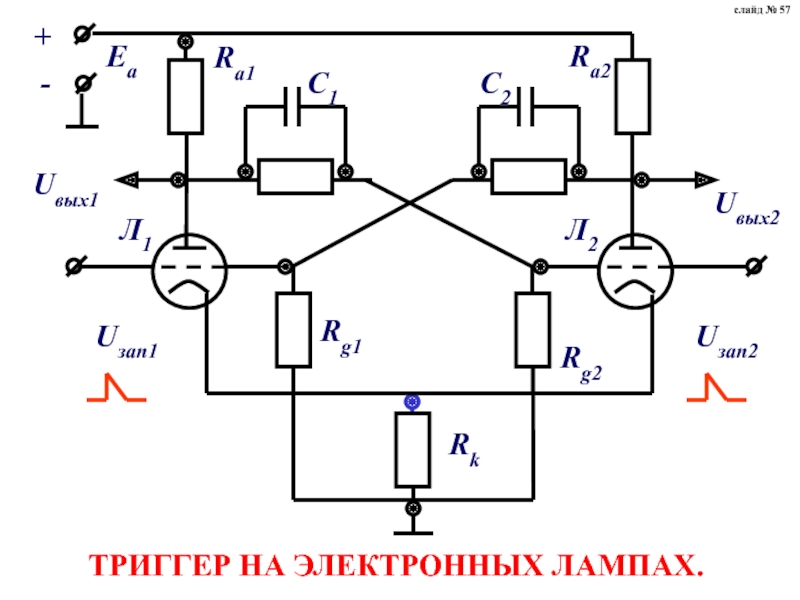

Здесь можно видеть два совершенно одинаковых синхронных RS-триггера, только для второго триггера синхроимпульсы инвертируются. Первый триггер в связке называют M (master) — хозяин, а второй триггер называется S (slave) — раб.

Допустим на входе «С» высокий потенциал. М-триггер принимает информацию, но низкий потенциал на входе синхронизации S-триггера блокирует приём информации. После того как потенциал поменялся на противоположный информация из M-триггера записывается в S-триггер, но приём информации в M-триггер блокируется.

Такая двухступенчатая система намного надёжнее обычного RS-триггера. Она свободна от случайных срабатываний.

Она свободна от случайных срабатываний.

Для более наглядного изучения работы RS-триггера рекомендую провести эксперименты с RS-триггером.

Главная » Цифровая электроника » Текущая страница

Также Вам будет интересно узнать:

Триггеры Текст научной статьи по специальности «Электротехника, электронная техника, информационные технологии»

УДК 621.37, 621.39

К.И. Волошиновский

ТРИГГЕРЫ

Работа над топологией триггера заставляет получить триггер наиболее надежный и при этом более простой, а сам синтез триггера заставляет задуматься о поэтапном закономерном получении схемы и математической модели триггера, чтобы за длительный интервал не накапливалась ошибка. Задача получения триггера без насыщения приводит к «целой» вариации решений на базе дискретных и непрерывных элементов. Область применения триггеров широка, в частности они применяются в устройствах преобразования данных в формате Манчестер. например в триггер-преобразователях ячеек AIT MIL STD 1553 для станций National Instruments PXI. При разработке практических задач схемы решений оказываются громоздкими [5], поэтому вспомогательные блоки должны быть заранее проработаны в виде готовых схемотехнических решений, в т.ч. для триггера. Использование триггера может быть востребовано даже в тестовой задаче.

Область применения триггеров широка, в частности они применяются в устройствах преобразования данных в формате Манчестер. например в триггер-преобразователях ячеек AIT MIL STD 1553 для станций National Instruments PXI. При разработке практических задач схемы решений оказываются громоздкими [5], поэтому вспомогательные блоки должны быть заранее проработаны в виде готовых схемотехнических решений, в т.ч. для триггера. Использование триггера может быть востребовано даже в тестовой задаче.

Ключевые слова: триггер, двоичный, троичный, на непрерывных элементах, схемотехническое решение.

Введение

В процессе схемотехнического синтеза триггера не ставится задача получить простую схему, важно получить схему которая технически реализуема и может быть представлена в виде топологии. В ряде источников, например в [7], в состав

Constants

Рис. 1. Применяемые схемы элементарной логики

1. Применяемые схемы элементарной логики

ISSN 0236-1493. Горный информационно-аналитический бюллетень. 2017. № 2. С. 24-45. © 2017. К.И. Волошиновский.

Рис. 2. Многотактный триггер на непрерывных элементах с коррекцией первого такта с помощью однотактного триггера в форсирующей связи

схемы включаются другие блоки, которые имеют собственные внутренние топологии, что усложняет задачу получения оконечной топологии, т.е. еще до того как задача решена, в состав

И 0ut GLOBAL 1 о I El ийЫ’

fi>I а и ш 0 в

аии еа-ч?

П 1 п h п п n h п

1

. 51-1-i-1-1-1-1-i-1-1-

51-1-i-1-1-1-1-i-1-1-

t 2 4 С * 11 12 U 1С 11 2*

Рис. 3. Переходные процессы в триггере на непрерывных элементах

схемы включаются готовые громоздкие блоки. Важно получить не однотактовое срабатывание, а множественное переключение разными способами с возможностью перезагрузки, причем таким образом, чтобы структура схемотехнического решения была прозрачно и было понятно из каких укрупненных блоков состоит оконечная схема.

Простейшая идея для получения схемотехнического решения триггера на непрерывных блоках получить контур, который хранит знак переключения на следующем такте, однако, как будет показано, такой подход приводит к схеме более громоздкой, но топология такой схемы не очень-то и громоздкая, поэтому есть смысл. Второй контур накапливает бит информации, который меняется под воздействие переключателя. Двух-контурная схема не так уж и сложна. Контур хранения знака можно построить по-разному, в том числе, применяя формулу замкнутой ПФ САУ.

Двух-контурная схема не так уж и сложна. Контур хранения знака можно построить по-разному, в том числе, применяя формулу замкнутой ПФ САУ.

Триггер на непрерывных элементах. Многотакный и однотакный в составе многотактного

Топология триггера делает интересными решения на простых блоках, которые имеют стандартные схемы аппаратной реализации. Реализация триггера — объект авторского права, поэтому решение должно с одной стороны отличаться от известных, но с другой стороны быть похожей на известные признанные решения, поэтому нельзя ограничиться рассмотрением одной или двух схем.

Рис. 4. Коррекция первого такта форсирующей связью с операционным усилителем в триггере на непрерывных элементах

На рис. 3. показано, что интервал поступления импульсов может варьироваться. Переходные процессы приведены для постоянного минимального квантования, однако саму схему можно проверить для переменной частоты следования импульсов на входе. аЬ 2007R, 2013. 2014 счетчик накопитель можно построить на дис-

аЬ 2007R, 2013. 2014 счетчик накопитель можно построить на дис-

Рис. 5. Переходные процессы и схема двоичного триггера

Constants

Рис. 6. Схема двоичного триггера с ровными прямоугольными фронтами импульсов

Рис. 7. Переходные процессы в схеме (рис. 6)

кретных блоках, что позволяет легко выровнять переходные процесс и получить «идеально-ровные» фронты импульсов.

Формульный триггер для MSExcel

Постановку задачи триггера в виде формулы можно представить в виде алгоритма программы MSExcel VBA:

Public Function TriggerF(I As Variant, O As Variant) As Variant ‘ returns Onew

‘ Идея в том, чтобы не сравнивать старое значение с новым,

‘ а подсчитать вектор по формуле

vector = I * (1 — O * 2)

Onew = O + vector

TriggerF = Onew

End Function

Рис. 8. Диаграмма (график) срабатывания формулы триггера в MSExcel

8. Диаграмма (график) срабатывания формулы триггера в MSExcel

Двочный триггер со переменной полярностью на входе и меандрой на выходе

Задача получения смены и поддержания единичного и нулевого уровня на выходе САУ значительно упрощается при обеспечении смены полярности по входу, но следует понимать, что смену полярности по входу сначала требуется обеспечить.

Рис. 9. Триггер с поддержание уровня на выходе при смене полярности на входе

□

Рис. 10. Два такта разной полярности на выходе двухтактного триггера

Двухтактный триггер на непрерывных элементах

В основу схемы многотактного триггера можно положить 3-тактный триггер. Такой подход предает схеме возможность многократного срабатывания, но не исключает аппаратного насыщения. Однако, прежде чем получить три такта сначала нужно получить два такта.

Такой подход предает схеме возможность многократного срабатывания, но не исключает аппаратного насыщения. Однако, прежде чем получить три такта сначала нужно получить два такта.

Рис. 11. 3-тактный триггер

Рис. 12. 3-тактный триггер: переходные процессы входа, вектора, выхода

Трехтактный триггер на непрерывных элементах

Триггер (рис. 2) построен на базе 3-тактного триггера (рис. 10).

Полнотактный триггер (w-тактный триггер) с блоком

округления

Иногда я-тактный триггер удается построить на базе 2-такт-ного триггера. Однако, один из необходимых блоков оказывается более сложным, например блок округления Floor. Идея такой схемы состоит в том, что после срабатывания сразу перевести вектор в ноль, т. е. не переключать вектор. Для такой схемы можно предложить другой инвертор.

е. не переключать вектор. Для такой схемы можно предложить другой инвертор.

Cciiitanll Soope2

л a 0j»> j а а @\ в а -щ

—Р 1 1 1- 1 —

1_ _ _

-(

Рис. 13. Триггер с блоком округления

Рис. 14. Триггер с амплитудой A

Рис. 15. Триггерная схема со «сложным» триггер-эффектом

Триггер с амплитудой A, хранящий sgn входного сигнала с прошлого такта

Триггер можно построить для случайного входа, применяя формулу замкнутой ПФ САУ, такой триггер хранит знак последнего не нулевого входного сигнала. А в течении интервала с нулевом входом, определенный знак поддерживается по выходу (рис. 14).

А в течении интервала с нулевом входом, определенный знак поддерживается по выходу (рис. 14).

Триггер-эффект c алгоритмом для его наблюдения и триггер на его основе

Часто возникает вопрос, как проиллюстрировать, и как получается, сложный триггер эффект, и как сложный триггер-эффект применить. Триггер эффект можно получить, например, с помощью схемы (рис. 15). Найденный триггер-эффект можно превратить в триггер (рис. 16).

Однотактный двоичный триггер с интегратором (операционным усилителем) в прямом тракте

См. рис. 17.

Рис. 16. Алгоритм двухтактоного триггера в среде MatLab2007b на базе триггер-эффекта

Рис. 17. Двоичный триггера с операционным усилителем Троичный триггер

Счетчик двоичного триггера можно применить для компактного троичного триггера.

Рис. 18. Троичный триггер просто считает 0, 1, 2; 0, 1, 2

Рис. 19. Троичный триггер на базе интегратора с перезагрузкой Троичный триггер с ровным прямоугольным фронтом

Рис. 20. Троичный триггер с ровными прямоугольным фромнтами

Двоичный триггер на базе интегратора

Рис. 21. Триггер с интегратором и quantizer

Триггер на базе блоков дискретного запаздывания

Рис. 22. Триггер с двумя запаздываниями при соблюдении нормированной длительности

Триггер с амплитудой А с «меандрой» переменной частоты без счетчика

_ ____Ос* РгооисМ ___

Ш-ЧЗ нэ

Н*дг»*. ог 5с©р«5 |__|

ог 5с©р«5 |__|

~<Г—

Рис. 23. Валидный трапециидальный выход триггера с амплитудой А<=1

Двоичный триггер на базе триггера с амплитудой А с меандрой переменной частоты со счетчиком

Рис. 24. Образование апериодического процесса, близкого к меандре, на производной после интегратора в триггерной схеме

Полуторатактный триггер («полтора такта»)

Прежде чем получить полноценный много тактовый триггер с обеспечением смены полярности на промежуточном входе второго контура, получим «полтора такта».

Рис. 25. 1,5-тактный триггер

Четырехтактный триггер со сменой полярности на промежуточном входе второго контура

: Ы а -ч Егы

Рис. 26. Четырехтактный триггер с необходимостью корректировки первого такта

Рис. 27. Четырехтактовый промежуточный выход для «триггера с амплитудой А» с математическая моделью [6] и сменой полярности

Двоичный триггер на базе триггера с амплитудой А

Рис. 28. Двоичный триггер на базе «триггера с амплитудой А»

Двоичный триггер на базе апериодического звена

На базе емкости, т.е. по сути апериодического звена с обратной связью, можно построить счетчик.

Рис. 29. Счетчик организованный на апериодическом звене с обратной связью

Из счетчика легко получить один такт, а затем превратить его в многотактный триггер.

Рис. 30. Двоичный однотактовый триггер с необходимостью корректировки первого такта на базе апериодического звена

Многотактный триггер со сменой полярности на промежуточном входе

Рис. 31. Многотактный триггер

‘§« И1* А «1

1 3 2 1 • •2 •3 1

1 11111

1 23456719 11

Рис. 32. Переходные процессы на выходах многотактного триггера

Рис. 33. Смена полярности на промежуточном входе

Триггер с возможностью перезагрузки на непрерывных элементах

Рис.ЧАВВ! е А и

1 0 -1 •2

II

г 4 в 8 10 12 14 16 18 20

Рис. 36. Импульсный сигнал входа перезагрузки 42

Многотактный триггер со сменой полярности на промежуточном входе без блока round

Рис. 37. Многотактный триггер со сменой полярности промежуточного входа «триггера с амплитудой А» без блока round

Заключение

Задача получения схемотехнического решения триггера решаема, даже для компактных топологий. Сложные блоки округления и дискретизации можно исключить из схемотехнического решения и представить его в виде схемы на непрерывных элементах, которая может быть реализована, хотя бы на микросхемах с целью аппаратной проверки и выявления аппаратных особенностей работы таких схем.

g® и«* i

1 3 2 1 • -1 •2 •3 •4 !

1 I I I

J 1 234567191

Рис. 38. Переходные процессы в триггере без блока round

В целом можно выделить триггеры двоичные (троичные, я-ичные) со счетчиком и без, с ровным и трапециидальными фронтами; на непрерывных элементах двухконтурные, с накоплениям вектора смены знака, с корректирокой первого такта форсирующей связью и накоплением бита; триггеры с обратной связью. Могут быть построены триггеры на базе интеграторов и апериодического звена, так же как и счетчики. Элементами схемы могут быть условные операторы сравнения чисел по величине, а также логические инверторы. В процессе корректировки первого бита можно использовать разные решения для однотактного триггера, приведенные выше.

Для громоздких схем в NI LabView или Step7 можно предложить алгоритмы для программной реализации триггеров на базе контроллеров Siemens, станций National Instruments PXI, а также любых других контроллеров, микропроцессоров и/или макетно-отладочных плат, что позволяет программно проверить предлагаемое решение триггера, а затем закономерно реализовать его аппаратно.

СПИСОК ЛИТЕРАТУРЫ

1. Волошиновский К. И. Свидетельство об официальной регистрации программы для ЭВМ № 2015619051, 24 августа 2015 г. Переключательные триггеры на непрерывных элементах и двоичные (Matlab Simulink).

2. Волошиновский К. И. Свидетельство об официальной регистрации программы для ЭВМ № 2016613022, 15 марта 2016 г. Программный комплекс: Триггеры: 2-х и n-тактные, троичный, с амплитудой А (sgn) и триггер-эффект (Matlab Simulink).

3. Волошиновский К. И. Заявка на государственную регистрацию программы для ЭВМ № 2016611276/69, 10.02.2016 г. Триггеры: многотакт-ные, 1- и 2-х тактные на базе 1/s и 1/Tp+1, без 1/s и с чередованием полярности на входе (Matlab Simulink).

4. Волошиновский К. И. Заявка № 206108645 от 11.03.2016. на государственную регистрацию заявления о выдаче патента Российской Федерации на изобретение: Способ преобразования электрических импульсов в код Манчестер и устройство для его осуществления.

5. Волошиновский К. И. Свидетельство об официальной регистрации программы для ЭВМ № 2016611624, 08 февраля 2016 г. Прозвон клемм-ных соединений (LabView).

6. Деч Г. Руководство к практическому применению преобразования Лапласа и z-Преобразования с приложением таблиц, составленных Р. Гершелем. — М.: Наука, 1971. — 288 с.

7. Зельдин Е. А. Триггеры. — М.: Энергоатомиздат, 1983. — 96 с.

8. Китов А. И., Криницкий Н. А. Электронные цифровые машины и программирование. — М.: Физматгиз, 1959. — 572 с. КПЗ

КОРОТКО ОБ АВТОРЕ

Волошиновский Кирилл Иванович — кандидат технических наук, доцент, e-mail: [email protected], МГИ НИТУ «МИСиС».

UDC 621.37, 621.39

Gornyy informatsionno-analiticheskiy byulleten’. 2017. No. 2, pp. 24-45. K.I. Voloshinovskiy

TRIGGERS

Elaboration of a layout of a trigger makes it possible to produce the most reliable and simpler trigger, and the process of synthesizing a trigger engenders thinking on step-by-step regular construction of a scheme and a mathematical model of a trigger, such that a longer interval brings no error accumulation. The task of obtaining a trigger without saturation leads to a variety of solutions based on discrete and continuous elements. Triggers have wide application area, for instance, in data conversion mechanisms using Manchester encoding, e.g. trigger-converters for PXI AIT MIL STD 1553 modules of National Instruments. Even the simplest solution schemes appear complicated when developing real-world problems [5], and auxiliary blocks and schemes are to be prepared beforehand, in the form of ready-made circuit decisions, including triggers. Trigger may be needed even in solving a test problem.

Key words: trigger, binary, ternary, continuous elements, circuit decision.

AUTHOR

Voloshinovskiy K.I., Candidate of Technical Sciences, Assistant Professor, e-mail: [email protected],

Mining Institute, National University of Science and Technology «MISiS», 119049, Moscow, Russia.

REFERENCES

1. Voloshinovskiy K. I. Svidetel’stvo ob ofitsial’noy registratsii programmy dlya EVM no 2015619051 (Certificate of official registration of computer programs no 2015619051),

24.08.2015.

2. Voloshinovskiy K. I. Svidetel’stvo ob ofitsial’noy registratsii programmy dlya EVM no 2016613022 (Certificate of official registration of computer programs no 2016613022),

15.03.2016.

3. Voloshinovskiy K. I. Zayavka na gosudarstvennuyu registratsiyu programmy dlya EVM no 2016611276/69 (Application for the state registration of the computer program no 2016611276/69), 10.02.2016.

4. Voloshinovskiy K. I. Zayavka na gosudarstvennuyu registratsiyu zayavleniya o vy-dache patenta Rossiyskoy Federatsii na izobretenie no 206108645 (Application for the state registration of applications for grant of a patent of the Russian Federation for the invention no 206108645), 11.03.2016.

5. Voloshinovskiy K. I. Svidetel’stvo ob ofitsial’noy registratsii programmy dlya EVM no 2016611624 (Certificate of official registration of computer programs no 2016611624), 08.02.2016.

6. Dech G. Rukovodstvo k prakticheskomu primeneniyu preobrazovaniya Laplasa i z-Preobrazovaniya sprilozheniem tablits, sostavlennykh R. Gershelem (A guide to the practical application of Laplace transform and z-transform with the application of tables, compiled by R. Herschel), Moscow, Nauka, 1971, 288 p.

7. Zel’din E. A. Triggery (Triggers), Moscow, Energoatomizdat, 1983, 96 p.

8. Kitov A. I., Krinitskiy N. A. Elektronnye tsifrovye mashiny iprogrammirovanie (Electronic digital machines and programming), Moscow, Fizmatgiz, 1959, 572 p.

Binary Firing System GenIII AR15 Trigger Pack

BFSIII® AR-C1 для платформы AR

Текущее время выполнения заказа 14+ недель

Binary Firing System® GEN 3 (BFSIII®) представляет собой 3-позиционный триггер. В позиции 3 он производит один выстрел при нажатии и один выстрел при отпускании, что делает этот спусковой крючок идеальным как для тактического, так и для соревновательного использования.BFSIII® значительно сокращает время перерыва между раундами, что позволяет играть в более плотных группах.

Срабатывание триггера:

Позиция 1 — Сейф — не срабатывает

Положение 2 — Полу — Стрельба по 1 выстрелу

Позиция 3 — Двоичная — стреляет 1 патрон при оттягивании и 1 патрон при выпуске

ОСОБЕННОСТИ:* Раунд выпуска можно отменить, просто переместив селектор «Ожидается получение патента» из режима Binary®, удерживая спусковой крючок назад

* Простота установки

* Плавное нажатие на спусковой крючок: 4.5 фунтов, +/- 0,5 фунта

* Положительный сброс на фазе разблокировки

* Улучшенные буферные пружины для оптимальной гибкости

* Работает на большинстве платформ и калибров AR, включая 5.56 NATO, 308 Win, 300 BLK, 9mm, Rimfire и т. Д.

* Совместимость с любым BCG

* Отлично подходит для стрелков-стрелков, стрелков-тактических стрелков и любителей активного отдыха

* AR-C1 поставляется со стандартным изогнутым спусковым крючком.

Отказ от прав и выпуск Binary Firing System®

Предупреждение:- Не для гражданских продаж в CA, CT, DC, FL, HI, IA, MD, NJ, NY, RI и WA

- In Delaware может использоваться только в пистолетных платформах.

- НИКОГДА НЕ ИЗМЕНЯЙТЕ ВНУТРЕННИЕ КОМПОНЕНТЫ BFS ™.

- Неправильная установка, использование или вмешательство в BFS ™ приведет к аннулированию гарантии и МОЖЕТ ПРИВЕСТИ К НЕПРЕДНАМЕРЕННОМУ РАЗРЯДУ ОРУЖИЯ, ЧТО МОЖЕТ ПРИВЕСТИ К ТРАВМАМ ИЛИ ДАЖЕ СМЕРТИ.

- После попытки установки возврат средств за триггеры производиться не будет.

- Приобретая этот продукт, вы принимаете на себя ответственность за исправность окончательной установки.

- ПОСЛЕ НАДЛЕЖАЩЕЙ УСТАНОВКИ BFS ™ ВСЕ ПОЛЬЗОВАТЕЛИ ОБЯЗАТЕЛЬНО ОБУЧАЮТ КВАЛИФИЦИРОВАННОЕ ОБУЧЕНИЕ ПО ИСПОЛЬЗОВАНИЮ ДАННЫХ ПРОДУКТОВ.

- Мы сотрудничаем с LMS Defense, чтобы предоставить 25% скидку на обучение. Те, кто завершит курс, получат код скидки 25% для использования при следующей покупке на этом сайте.

- Размер спускового штифта: 154 дюйма

- Нет 80% понижений, Нет полимеров, Нет карбона

- Патент № 9,952,012; 9,952,013; 10 107 580; 10 393 461; 10 480 881 и 10 480 882

Чрескожное отпускание большого пальца на спусковом крючке: безопасная техника пуш-пуля | Г.

Hazani R, Elston J, Whitney RD, Redstone J, Chowdhry S, Wilhelmi BJ. Безопасное лечение большого пальца спускового крючка с продольными анатомическими ориентирами.Эпластика. 2010; 10: 57.

Хуан Гонконг, Ван Дж. П., Линь Си Джей, Хуанг Ю. К., Хуанг Т.Ф., Чанг М.С. Сравнение краткосрочных и долгосрочных результатов после открытого или чрескожного высвобождения для триггерного пальца. Ортопедия. 2017; 40 (1): 131-5.

Quinnell RC. Консервативное лечение триггерного пальца. Практик. 1980; 224 (1340): 187-90.

Maneerit J, Sriworakun C, Budhraja N, Nagavajara P. Триггерный палец: результаты проспективного рандомизированного исследования чрескожного высвобождения с инъекцией стероидов по сравнению с инъекцией только стероидов.J Hand Surg Br. 2003. 28 (6): 586–9.

Gilberts EC, Wereldsma JC. Отдаленные результаты чрескожных и открытых операций на триггерных и больших пальцах. Int Surg. 2002; 87 (1): 48-52.